|   | Memory Banks                                                                                                                                                                                                                                                                                                                    |                    |                        |                                                                                        |  |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|----------------------------------------------------------------------------------------|--|--|

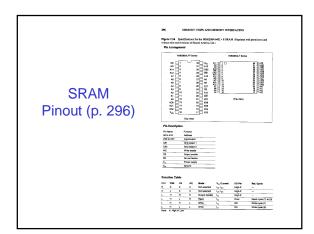

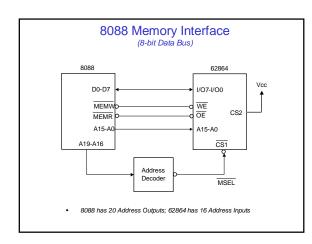

| • | 8086/186/286/386SX has 16 Data Lines D15-D0, HM62864 Only<br>Has 8 I/O7 – I/O0                                                                                                                                                                                                                                                  |                    |                        |                                                                                        |  |  |

| • | <ul> <li>Must Use a "Memory Bank"</li> <li>1 SRAM for Storing Bytes with "Even Addresses" ( 0<sub>2</sub>)</li> <li>1 SRAM for Storing Bytes with "Odd" Addresses" ( 1<sub>2</sub>)</li> <li>8086 has BHE Control Signal – (Bank High Enable)</li> <li>Can Use Combination of A0 and BHE to Determine Type of Access</li> </ul> |                    |                        |                                                                                        |  |  |

|   |                                                                                                                                                                                                                                                                                                                                 | BHE<br>0<br>1<br>1 | A0<br>0<br>1<br>0<br>1 | Access Type<br>1 word (16-bits)<br>Odd Byte (D15-D8)<br>Even Byte (D7-D0)<br>No Access |  |  |

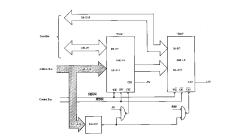

### 86,186,286,386SX Memory Interface

- Connect CPU A16-A1 Outputs to Memory Chip A15-A0 Inputs

- Use A0 and BHE to "Select" the Correct Memory Chip

- "Bank Select" Circuit

### **Misaligned Access**

• 1 Word = 16 bits - Can Have a Misaligned Access

| 1.1 |     | - Kaus - d |

|-----|-----|------------|

| MSB | LSB | Access     |

| odd | even | aligned |

|-----|------|---------|

|-----|------|---------|

- even odd misaligned

- Misaligned Words Require 2 Bus Cycles! (2)(2.3T)=4.6T

1) Access LSB (odd) Byte on D15-D8

- 2) Access MSB (even) Byte on D7-D0

- "Aligning" Program Data Can Speed Up Execution

- "Wastes" Memory (fragments RAM)

- Most Optimizing Compilers do it Automatically

- Up to Assembler Language Programmer

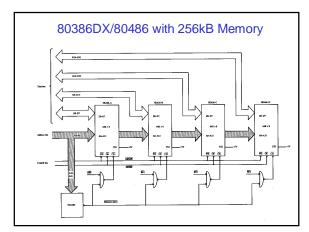

## 80386DX and 80486 Memory Interface (32 bit)

- 4 Banks of Byte-Wide RAM Required

- With HM62864 Minimum Memory Size is 256kB

- need 4 of these 64k×8 Chips

- These Processors are Restricted to Aligned Access

- Do Not Have A1, A0 Pins

- Do Have BE3, BE2, BE1, BE0 (Byte Enables)

- Memory Bank is Selected Using the Byte Enable Signals

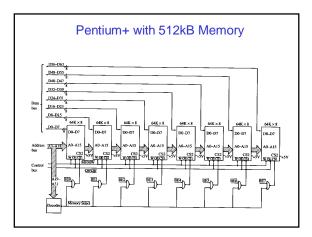

# Pentium+ Memory Interface

- 8 Banks of Byte-Wide RAM Required

- With HM62864 Minimum Memory Size is512kB

- need 8 of these 64k×8 Chips

- at least 1 chip per bank (byte)

- These Processors are Restricted to Aligned Access

- Do Not Have A2, A1, A0 Pins

- Do Have BE7 BE0 (Byte Enables)

- Memory Bank is Selected Using the Byte Enable Signals

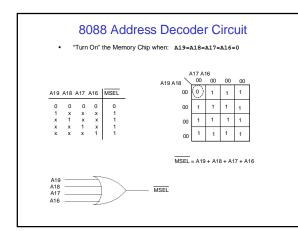

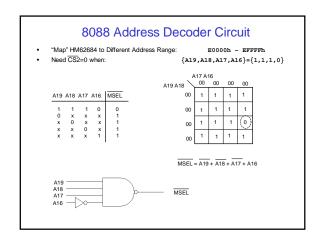

### Address Decoding

#### General

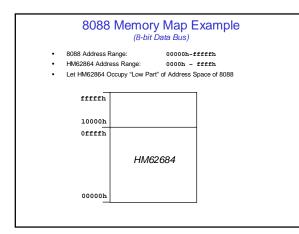

- 1) MS Address Lines Used as Decoder Inputs

- 2) LS Address Lines Used to Select Memory Banks

- 3) "Middle Address Lines" Connected Directly to Memory Chip Address Inputs

- Address Decoder

- Circuit with MS Address Lines as Inputs

- Output is the Chip Select (CS) Signal(s)

- Address Decoder Logic "Decides" Where Memory is

- Located

- Memory Map

- Book Reviews Logic Design PALs, CUPL, etc. Read This On Your Own

| XT Memory Map    |                    |                                                   |  |  |  |  |

|------------------|--------------------|---------------------------------------------------|--|--|--|--|

| 00000h           | IVT                | "Interrupt Vector Table"                          |  |  |  |  |

| 00400h           | BIOS DATA          | "keyboard status bytes, disk parm. tables, etc."  |  |  |  |  |

| 00500h           | DOS/BASIC Reserved | "COMMAND.COM, IO.SYS, MSDOS.SYS"                  |  |  |  |  |

| 00600h           | USER<br>Space      | "Application Programs and Data"                   |  |  |  |  |

| A0000h           | Video<br>Buffer    | "Dual-Port RAM Containing Display Pages"          |  |  |  |  |

| C0000h           | BIOS<br>Expansions | "EGA BIOS, PGA Comm., XT HD, etc."                |  |  |  |  |

| E0000h           | BIOS<br>Extensions | "SCSI Controller Card BIOS, NIC BIOS, etc. – ROM" |  |  |  |  |

| F0000h<br>FFFFFh | ROM<br>BIOS        | "POST, Bootstrap, ROM-BIOS ISRs"                  |  |  |  |  |

|                  |                    |                                                   |  |  |  |  |