# **HiRel FPGAs**

#### **Features**

- Highly Predictable Performance with 100 Percent Automatic Placement and Routing

- Device Sizes from 1200 to 20,000 gates

- Up to 6, Fast, Low-Skew Clock Networks

- Up to 202 User-Programmable I/O Pins

- More Than 500 Macro Functions

- Up to 1276 Dedicated Flip-Flops

- I/O Drive to 10 mA

- · Devices Available to DSCC SMD

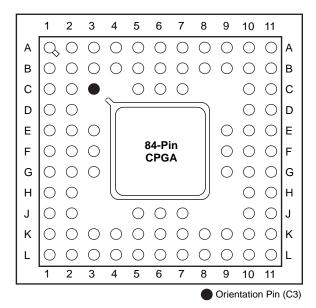

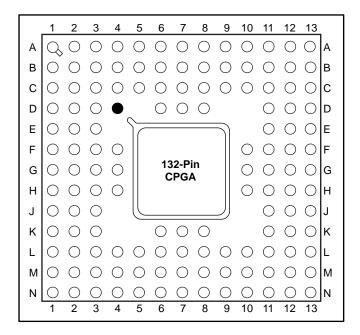

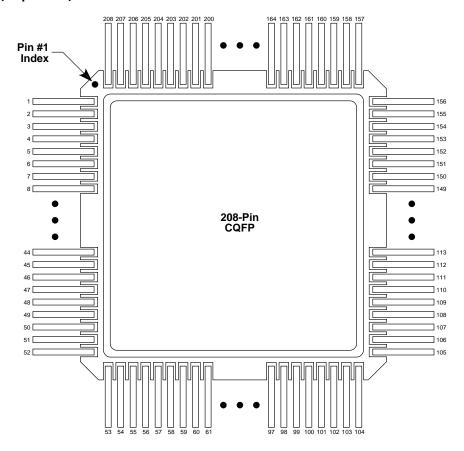

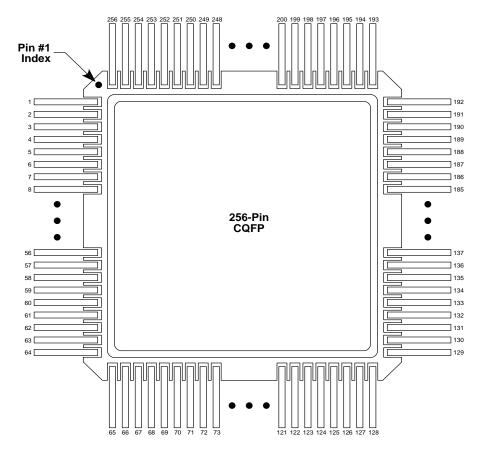

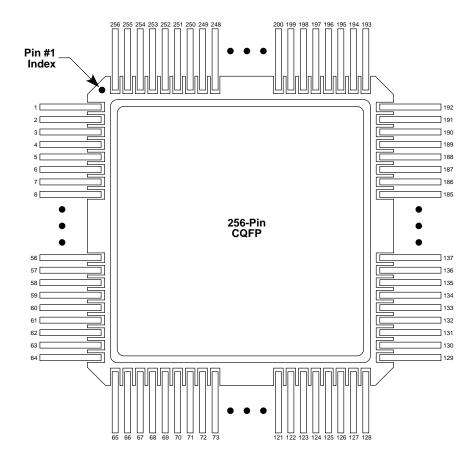

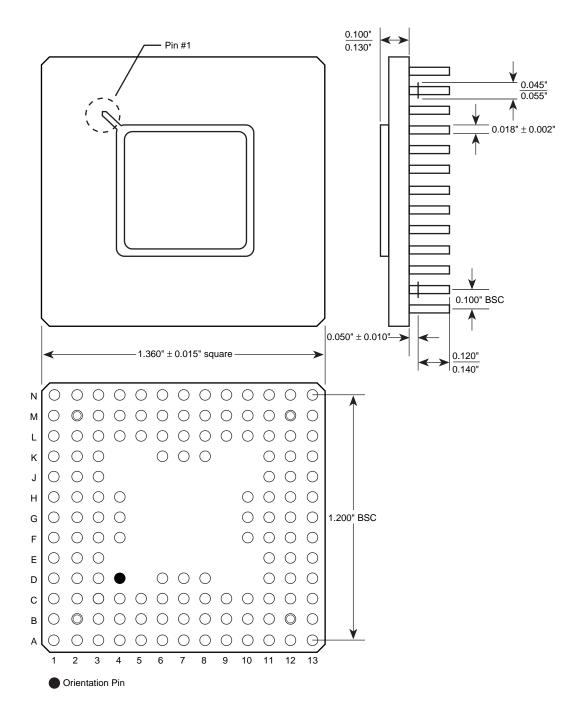

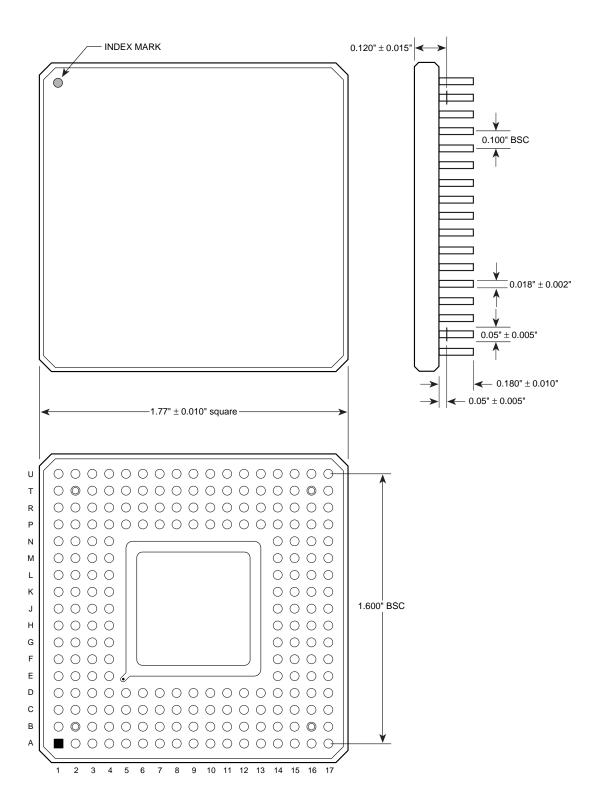

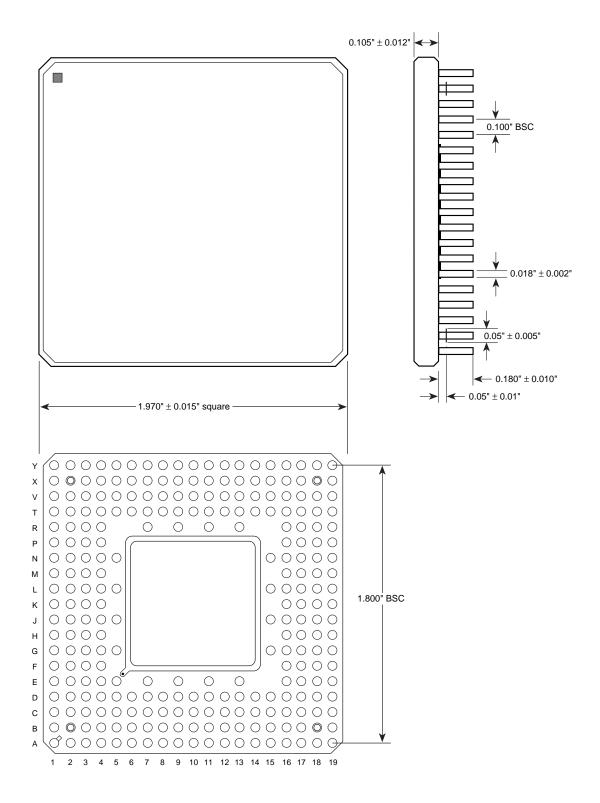

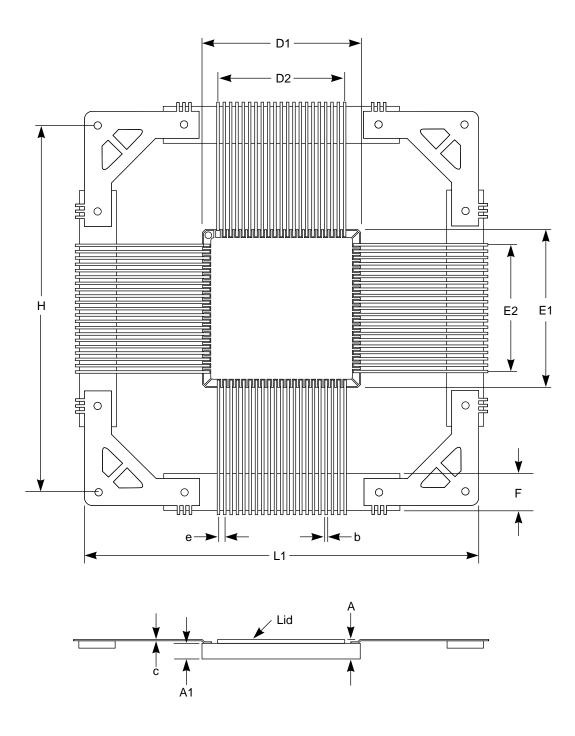

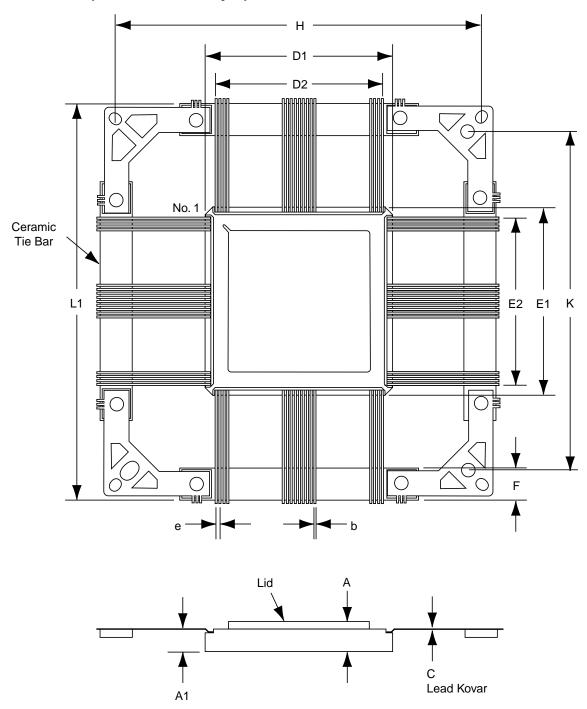

- CQFP and CPGA Packaging

- Nonvolatile, User Programmable

- Logic Fully Tested Prior to Shipment

#### **ACT 3 Features**

- Highest-Performance, Highest-Capacity FPGA Family

- System Performance to 60 MHz over Military Temperature

- Low-Power 0.8-micron CMOS Technology

#### 3200DX

- 100 MHz System Logic Integration

- Highest Speed FPGA SRAM, up to 2.5 Kbits Configurable Dual-Port SRAM

- Fast Wide-Decode Circuitry

#### 1200XL Features

- Pin for Pin Compatible with ACT 2

- System Performance to 50 MHz over Military Temperature

- Low-Power 0.6-micron CMOS Technology

#### **ACT 2 Features**

- Best-Value, High-Capacity FPGA Family

- System Performance to 40 MHz over Military Temperature

- Low-Power 1.0-micron CMOS Technology

#### **ACT 1 Features**

- Lowest-Cost FPGA Family

- System Performance to 20 MHz over Military Temperature

- Low-Power 1.0-micron CMOS Technology

#### **Product Family Profile**

| Family                                            |                         | ACT 3                   |                          | 320                      | 0DX                        | 1200XL                    |

|---------------------------------------------------|-------------------------|-------------------------|--------------------------|--------------------------|----------------------------|---------------------------|

| Device                                            | A1425A                  | A1460A                  | A14100A                  | A32100DX                 | A32200DX                   | A1280XL                   |

| Capacity<br>Logic Gates<br>SRAM Bits              | 2,500<br>NA             | 6,000<br>NA             | 10,000<br>NA             | 10,000<br>2,048          | 20,000<br>2,560            | 8,000                     |

| Logic Modules<br>S-Modules<br>C-Modules<br>Decode | 310<br>160<br>150<br>NA | 848<br>432<br>416<br>NA | 1377<br>697<br>680<br>NA | 1362<br>700<br>662<br>20 | 2414<br>1230<br>1184<br>24 | 1,232<br>624<br>608<br>NA |

| Flip-Flops (maximum)                              | 435                     | 976                     | 1493                     | 738                      | 1276                       | 998                       |

| User I/Os (maximum)                               | 100                     | 168                     | 228                      | 152                      | 202                        | 140                       |

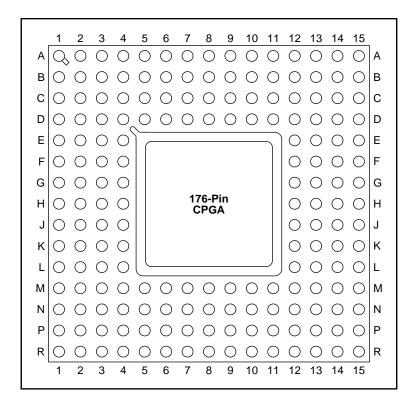

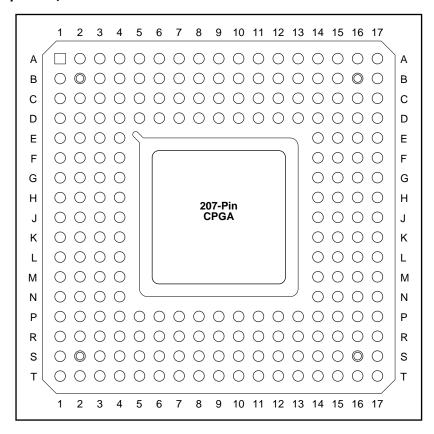

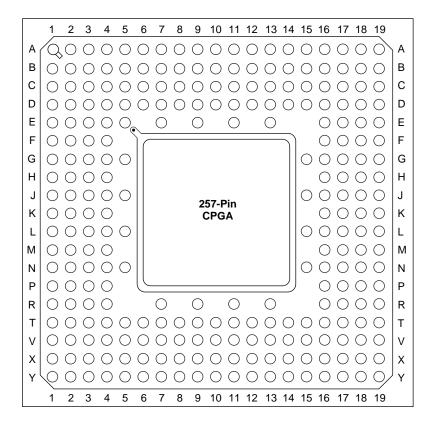

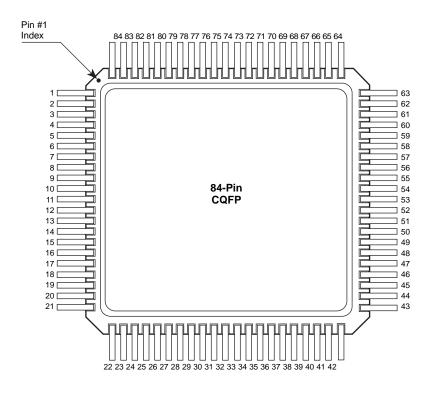

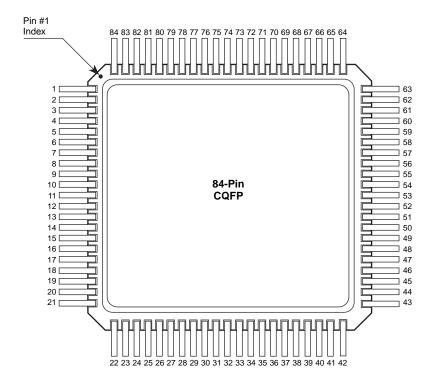

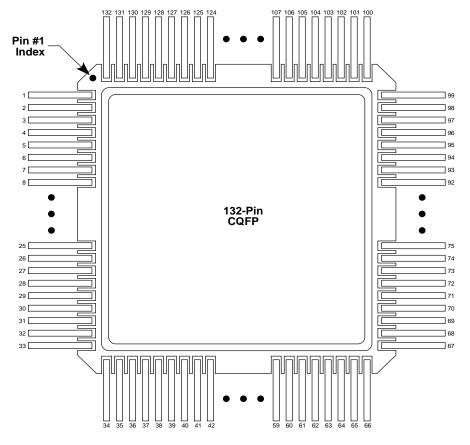

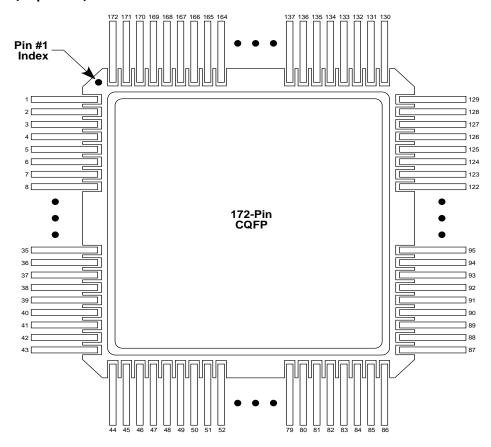

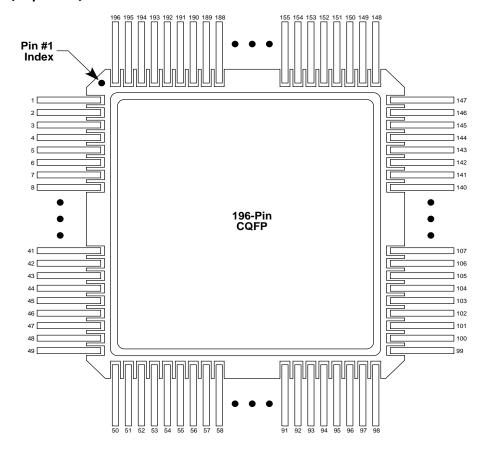

| Packages <sup>1</sup> (by pin count) CPGA CQFP    | 133<br>132              | 207<br>196              | 257<br>256               | 84                       | 208, 256                   | 176<br>172                |

| Performance<br>System Speed (maximum)             | 60 MHz                  | 60 MHz                  | 60 MHz                   | 55 MHz                   | 55 MHz                     | 50 MHz                    |

#### Note:

1. See Product Plan on page 6 for package availability.

## **Product Family Profile**

| Family                                            | ACT 2                   |                          | АСТ                   | 1                     |

|---------------------------------------------------|-------------------------|--------------------------|-----------------------|-----------------------|

| Device                                            | A1240A                  | A1280A                   | A1010B                | A1020B                |

| Capacity Logic Gates SRAM Bits                    | 4,000<br>NA             | 8,000<br>NA              | 1,200<br>NA           | 2,000<br>NA           |

| Logic Modules<br>S-Modules<br>C-Modules<br>Decode | 684<br>348<br>336<br>NA | 1232<br>624<br>608<br>NA | 295<br>—<br>295<br>NA | 547<br>—<br>547<br>NA |

| Flip-Flops (maximum)                              | 568                     | 998                      | 147                   | 273                   |

| User I/Os (maximum)                               | 104                     | 140                      | 57                    | 69                    |

| Packages <sup>1</sup> (by pin count) CPGA CQFP    | 132<br>—                | 176<br>172               | 84<br>—               | 84<br>84              |

| Performance<br>System Speed (maximum)             | 40 MHz                  | 40 MHz                   | 20 MHz                | 20 MHz                |

#### Note:

1. See Product Plan on page 6 for package availability.

## High-Reliability, Low-Risk Solution

Actel builds the most reliable field programmable gate arrays (FPGAs) in the industry, with overall antifuse reliability ratings of less than 10 Failures-In-Time (FITs), corresponding to a useful life of more than 40 years. Actel FPGAs have been production proven, with more than five million devices shipped and more than one trillion antifuses manufactured. Actel devices are fully tested prior to shipment, with an outgoing defect level of only 122 ppm. (Further reliability data is available in the "Actel Device Reliability Report.")

#### **100 Percent Tested**

Device functionality is fully tested before shipment and during device programming. Routing tracks, logic modules, and programming, debug, and test circuits are 100 percent tested before shipment. Antifuse integrity also is tested before shipment. Programming algorithms are tested when a device is programmed using Actel's Activator<sup>®</sup> 2 or Activator 2S programming stations.

#### **Benefits**

No Cost Risk—Once you have a Designer/Designer Advantage ™ System, Actel's CAE software and programming package, you can produce as many chips as you like for just the cost of the device itself, with no NRE charges to eat up your development budget every time you want to try out a new design.

No Time Risk—After entering your design, placement and routing is automatic, and programming the device takes only about 5 to 15 minutes for an average design. You save time in the design entry process by using tools that are familiar to you. The Designer/Designer Advantage System software interfaces with popular CAE packages such as Cadence, Mentor Graphics, OrCAD, and Viewlogic, running on platforms such as HP, Sun, and PC. In addition, synthesis capability is provided with support of synthesis tools from Synopsys, IST, Exemplar, and DATA I/O.

No Reliability Risk—The PLICE<sup>®</sup> antifuse is a one-time programmable, nonvolatile connection. Since Actel devices are permanently programmed, no downloading from EPROM or SRAM storage is required. Inadvertent erasure is impossible, and there is no need to reload the program after power disruptions. Fabrication using a low-power CMOS process means cooler junction temperatures. Actel's non-PLD architecture delivers lower dynamic operating current. Our reliability tests show a very low failure rate of 66 FITs at 90°C junction temperature with no degradation in AC performance. Special stress testing at wafer test eliminates infant mortalities prior to packaging.

No Security Risk—Reverse engineering of programmed Actel devices from optical or electrical data is extremely difficult. Programmed antifuses cannot be identified from a photograph or by using a SEM. The antifuse map cannot be deciphered either electrically or by microprobing. Each

device has a silicon signature that identifies its origins, down to the wafer lot and fabrication facility.

No Testing Risk—Unprogrammed Actel parts are fully tested at the factory. This includes the logic modules, interconnect tracks, and I/Os. AC performance is ensured by special speed path tests, and programming circuitry is verified on test antifuses. During the programming process, an algorithm is run to ensure that all antifuses are correctly programmed. In addition, Actel's Actionprobe<sup>®</sup> diagnostic tools allow 100 percent observability of all internal nodes to check and debug your design.

## **Actel FPGA Description**

The Actel families of FPGAs offer a variety of packages, speed/performance characteristics, and processing levels for use in all high-reliability and military applications. Devices are implemented in a silicon gate, two-level metal CMOS process, utilizing Actel's PLICE antifuse technology. This unique architecture offers gate array flexibility, high performance, and quick turnaround through user programming. Device utilization is typically 95 percent of available logic modules.

Actel devices also provide system designers with on-chip diagnostic probe/debug capability, allowing the user to observe 100 percent of the nodes within the design, even while the device is operating in-system. All Actel devices include on-chip clock drivers and a hard-wired distribution network.

User-definable I/Os are capable of driving at both TTL and CMOS drive levels. Available packages for the military are the Ceramic Quad Flat Pack (CQFP) and the Ceramic Pin Grid Array (CPGA). See Product Plan on page 6 for details.

All Actel FPGAs are supported by the Actel Designer Series, which offers automatic or user-definable pin assignment, validation of electrical and design rules, automatic placement and routing, timing analysis, user programming, and debug/diagnostic probe capabilities. The Designer Series fully supports schematic capture and backannotated simulation through design kits for Cadence, Mentor Graphics, OrCAD, and Viewlogic. Synthesis is supported with kits for use with synthesis tools from Synopsys, IST, Exemplar, and DATA I/O.

Also available is the ACTmap  $^{\text{TM}}$  VHDL optimization and synthesis tool that provides logic synthesis and optimization from PAL language or VHDL description inputs. An FPGA macro generator (ACTgen Macro Builder) is provided, allowing the user easily to create higher-level functions such as counters and adders. Finally, ChipEdit is a graphical/visual design tool that allows the user to modify the automatic place and route results.

#### **ACT 3 Description**

The ACT 3 family is the third-generation Actel FPGA family. This family offers the highest-performance and highest-capacity devices, ranging from 2,500 to 10,000 gates, with system performance to 60 MHz over the military temperature range. The devices have four clock distribution networks, including dedicated array and I/O clocks. In addition, the ACT 3 family offers the highest I/O-to-gate ratio available. ACT 3 devices are manufactured using 0.8 micron CMOS technology.

### 1200XL/3200DX Description

3200DX and 1200XL FPGAs were designed to integrate system logic which is typically implemented in multiple CPLDs, PALs and FPGAs. These devices provide the features and performance required for today's complex, high-speed digital logic systems. The 3200DX family offers the industry's fastest dual-port SRAM for implementing fast FIFOs, LIFOs and temporary data storage.

## **ACT 2 Description**

The ACT 2 family is the second-generation Actel FPGA family. This family offers the best-value, high-capacity devices, ranging from 4,000 to 8,000 gates, with system performance to 40 MHz over the military temperature range. The devices have two routed array clock distribution networks. ACT 2 devices are manufactured using 1.0 micron CMOS technology.

#### **ACT 1 Description**

The ACT 1 family is the first Actel FPGA family and the first antifuse-based FPGA. This family offers the lowest-cost logic integration, with devices ranging from 1,200 to 2,000 gates, with system performance to 20 MHz over the military temperature range. The devices have one routed array clock distribution network. ACT 1 devices are manufactured using 1.0 micron CMOS technology.

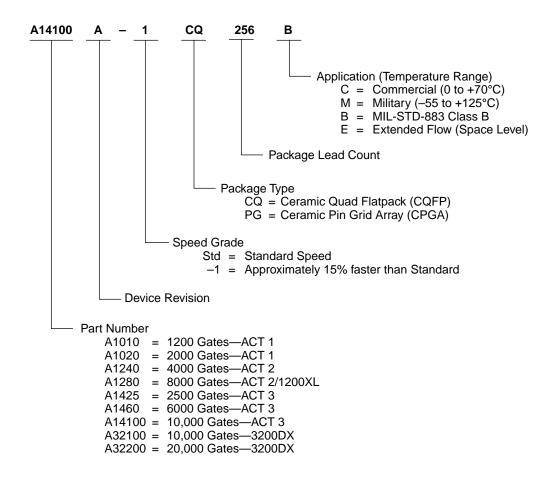

## **Military Device Ordering Information**

## **DESC SMD/Actel Part Number Cross Reference**

| Actel Part Number | DSCC SMD        | DSCC SMD        |

|-------------------|-----------------|-----------------|

| (Gold Leads)      | (Gold Leads)    | (Solder Dipped) |

| A1010B-PG84B      | 5962-9096403MXC | 5962-9096403MXA |

| A1010B-1PG84B     | 5962-9096404MXC | 5962-9096404MXA |

| A1020B-PG84B      | 5962-9096503MUC | 5962-9096503MUA |

| A1020B-1PG84B     | 5962-9096504MUC | 5962-9096504MUA |

| A1020B-CQ84B      | 5962-9096503MTC | 5962-9096503MTA |

| A1020B-1CQ84B     | 5962-9096504MTC | 5962-9096504MTA |

| A1240A-PG132B     | 5962-9322101MXC | 5962-9322101MXA |

| A1240A-1PG132B    | 5962-9322102MXC | 5962-9322102MXA |

| A1280A-PG176B     | 5962-9215601MXC | 5962-9215601MXA |

| A1280A-1PG176B    | 5962-9215602MXC | 5962-9215602MXA |

| A1280A-CQ172B     | 5962-9215601MYC | 5962-9215601MYA |

| A1280A-1CQ172B    | 5962-9215602MYC | 5962-9215602MYA |

| A1425A-PG133B     | 5962-9552001MXC | 5962-9552001MXA |

| A1425A-1PG133B    | 5962-9552002MXC | 5962-9552002MXA |

| A1425A-CQ132B     | 5962-9552001MYC | 5962-9552001MYA |

| A1425A-1CQ132B    | 5962-9552002MYC | 5962-9552002MYA |

| A1460A-PG207B     | 5962-9550801MXC | 5962-9550801MXA |

| A1460A-1PG207B    | 5962-9550802MXC | 5962-9550802MXA |

| A1460A-CQ196B     | 5962-9550801MYC | 5962-9550801MYA |

| A1460A-1CQ196B    | 5962-9550802MYC | 5962-9550802MYA |

| A14100A-PG257B    | 5962-9552101MXC | 5962-9552101MXA |

| A14100A-1PG257B   | 5962-9552102MXC | 5962-9552102MXA |

| A14100A-CQ256B    | 5962-9552101MYC | 5962-9552101MYA |

| A14100A-1CQ256B   | 5962-9552102MYC | 5962-9552102MYA |

| A32100DX-CQ84B    | TBD             | TBD             |

| A32100DX-1CQ84B   | TBD             | TBD             |

| A32200DX-CQ208B   | TBD             | TBD             |

| A32200DX-1CQ208B  | TBD             | TBD             |

## **Product Plan**

|                                       | Speed    | Grade     | Application |          |          |          |

|---------------------------------------|----------|-----------|-------------|----------|----------|----------|

| 3200DX Family                         | Std      | <b>–1</b> | С           | М        | В        | E        |

| A32100DX Device                       |          |           |             |          |          |          |

| 84-pin Ceramic Quad Flatpack (CQFP)   | <b>V</b> | <b>✓</b>  | <b>V</b>    | <b>'</b> | <b>V</b> | _        |

| A32200DX Device                       |          |           |             |          |          |          |

| 208-pin Ceramic Quad Flatpack (CQFP)  | V        | <b>✓</b>  | <b>V</b>    | <b>V</b> | <b>V</b> | _        |

| 256-pin Ceramic Quad Flatpack (CQFP)  | ✓        | ✓         | ✓           | ✓        | ✓        | _        |

| ACT 3 Family                          |          |           |             |          |          |          |

| A1425A Device                         |          |           |             |          |          |          |

| 132-pin Ceramic Quad Flatpack (CQFP)  | <b>✓</b> | <b>V</b>  | <b>V</b>    | ~        | <b>/</b> | _        |

| 133-pin Ceramic Pin Grid Array (CPGA) | <b>✓</b> | ~         | ✓           | ~        | ~        |          |

| A1460A Device                         |          |           |             |          |          |          |

| 196-pin Ceramic Quad Flatpack (CQFP)  | <b>V</b> | <b>✓</b>  | ~           | <b>V</b> | <b>V</b> | _        |

| 207-pin Ceramic Pin Grid Array (CPGA) | <b>✓</b> | <b>✓</b>  | ~           | •        | <b>✓</b> | _        |

| A14100A Device                        |          |           |             |          |          |          |

| 256-pin Ceramic Quad Flatpack (CQFP)  | <b>V</b> | <b>✓</b>  | ~           | <b>V</b> | <b>V</b> | _        |

| 257-pin Ceramic Pin Grid Array (CPGA) | <b>✓</b> | <b>✓</b>  | ~           | •        | <b>✓</b> | _        |

| 1200XL Family                         |          |           |             |          |          |          |

| A1280XL Device                        |          |           |             |          |          |          |

| 172-pin Ceramic Quad Flatpack (CQFP)  | <b>V</b> | <b>✓</b>  | ~           | <b>V</b> | <b>V</b> | _        |

| 176-pin Ceramic Pin Grid Array (CPGA) | <b>✓</b> | <b>V</b>  | ~           | •        | <b>✓</b> | _        |

| ACT 2 Family                          |          |           |             |          |          |          |

| A1240A Device                         |          |           |             |          |          |          |

| 132-pin Ceramic Pin Grid Array (CPGA) | <b>V</b> | <b>V</b>  | <b>~</b>    | <b>'</b> | <b>V</b> | _        |

| A1280A Device                         |          |           |             |          |          |          |

| 172-pin Ceramic Quad Flatpack (CQFP)  | <b>V</b> | <b>V</b>  | <b>V</b>    | <b>'</b> | <b>V</b> | <b>V</b> |

| 176-pin Ceramic Pin Grid Array (CPGA) | <b>✓</b> | <b>V</b>  | ~           | •        | <b>✓</b> | <b>✓</b> |

| ACT 1 Family                          |          |           |             |          |          |          |

| A1010B Device                         |          |           |             |          |          |          |

| 84-pin Ceramic Pin Grid Array (CPGA)  | <b>✓</b> | ·         | <b>✓</b>    | ~        | ~        | _        |

| A1020B Device                         |          |           |             |          |          |          |

| 84-pin Ceramic Quad Flatpack (CQFP)   | <b>✓</b> | <b>✓</b>  | <b>✓</b>    | ~        | ~        | <b>✓</b> |

| 84-pin Ceramic Pin Grid Array (CPGA)  | <b>✓</b> | ~         | ✓           | ~        | •        | ~        |

Applications: C = Commercial Availability: ✓ = Available Now Speed Grade:-1=Approx. 15% faster than Standard

M = Military P = Planned B = MIL-STD-883 — = Not Planned

E = Extended Flow

#### **3200DX Device Resources**

|             |                  |                     | User I/Os              |  |  |  |

|-------------|------------------|---------------------|------------------------|--|--|--|

| FPGA        | Logio            | Gate Array          | CQFP                   |  |  |  |

| Device Type | Logic<br>Modules | Equivalent<br>Gates | 84-pin 208-pin 256-pin |  |  |  |

| A32100DX    | 1362             | 10,000              | 60 — —                 |  |  |  |

| A32200DX    | 2414             | 20,000              | — 176 202              |  |  |  |

## **ACT 3 Device Resources**

|             |                  |                     | User I/Os |         |         |         |         |         |

|-------------|------------------|---------------------|-----------|---------|---------|---------|---------|---------|

| FPGA        | Logio            | Gate Array          |           | CQFP    |         |         | CPGA    |         |

| Device Type | Logic<br>Modules | Equivalent<br>Gates | 132-pin   | 196-pin | 256-pin | 133-pin | 207-pin | 257-pin |

| A1425A      | 310              | 2500                | 100       | _       | _       | 100     | _       | _       |

| A1460A      | 848              | 6000                | _         | 168     | _       | _       | 168     | _       |

| A14100A     | 1377             | 10,000              | _         | _       | 228     | _       | _       | 228     |

#### **1200XL Device Resources**

|             |                  |                          | Us      | er I/Os |

|-------------|------------------|--------------------------|---------|---------|

| FPGA        | Logio            | Gate Array<br>Equivalent | CQFP    | CPGA    |

| Device Type | Logic<br>Modules | Gates                    | 172-pin | 176-pin |

| A1280XL     | 1232             | 8000                     | 140     | 140     |

## **ACT 2 Device Resources**

|                     |                  |                     | User I/Os |         |         |

|---------------------|------------------|---------------------|-----------|---------|---------|

| EDCA                | Lagia            | Gate Array          | CQFP      | СР      | GA      |

| FPGA<br>Device Type | Logic<br>Modules | Equivalent<br>Gates | 172-pin   | 132-pin | 176-pin |

| A1240A              | 684              | 4000                | _         | 104     | _       |

| A1280A              | 1232             | 8000                | 140       | _       | 140     |

## **ACT 1 Device Resources**

|             |         |                          | User I/Os |        |  |

|-------------|---------|--------------------------|-----------|--------|--|

| FPGA        | Logic   | Gate Array<br>Equivalent | CQFP      | CPGA   |  |

| Device Type | Modules | Gates                    | 84-pin    | 84-pin |  |

| A1010B      | 295     | 1200                     | _         | 57     |  |

| A1020B      | 547     | 2000                     | 69        | 69     |  |

# **Pin Description**

## CLK Clock (Input)

ACT 1 only. TTL Clock input for global clock distribution network. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

# CLKA Clock A (Input)

ACT 3, 1200XL, and ACT 2 only. TTL Clock input for global clock distribution networks. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

#### CLKB Clock B (Input)

ACT 3, 1200XL, and ACT 2 only. TTL Clock input for global clock distribution networks. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

#### DCLK Diagnostic Clock (Input)

TTL Clock input for diagnostic probe and device programming. DCLK is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### GND Ground

LOW supply voltage.

# HCLK Dedicated (Hard-wired) Array Clock (Input)

ACT 3 only. TTL Clock input for sequential modules. This input is directly wired to each S-module and offers clock speeds independent of the number of S-modules being driven. This pin can also be used as an I/O.

## I/O Input/Output (Input, Output)

I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/O pins are automatically driven LOW.

# IOCLK Dedicated (Hard-wired) I/O Clock (Input)

ACT 3 only. TTL Clock input for I/O modules. This input is directly wired to each I/O module and offers clock speeds independent of the number of I/O modules being driven. This pin can also be used as an I/O.

# IOPCL Dedicated (Hard-wired) I/O Preset/Clear (Input)

ACT 3 only. TTL input for I/O preset or clear. This global input is directly wired to the preset and clear inputs of all I/O registers. This pin functions as an I/O when no I/O preset or clear macros are used.

#### MODE Mode (Input)

The MODE pin controls the use of diagnostic pins (DCLK, PRA, PRB, SDI). When the MODE pin is HIGH, the special functions are active. When the MODE pin is LOW, the pins function as I/Os. When the MODE pin is LOW, the pins function as I/Os. To provide Actionprobe capability, the MODE pin should be terminated to GND through a 10K resistor so that the MODE pin can be pulled high when required.

#### NC No Connection

This pin is not connected to circuitry within the device.

#### PRA/I/O Probe A (Output)

The Probe A pin is used to output data from any user-defined design node within the device. This independent diagnostic pin can be used in conjunction with the Probe B pin to allow real-time diagnostic output of any signal path within the device. The Probe A pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRA is accessible when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### PRB/I/O Probe B (Output)

The Probe B pin is used to output data from any user-defined design node within the device. This independent diagnostic pin can be used in conjunction with the Probe A pin to allow real-time diagnostic output of any signal path within the device. The Probe B pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRB is accessible when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

## SDI Serial Data Input (Input)

Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

# V<sub>CC</sub> 5V Supply Voltage

HIGH supply voltage.

#### QCLKA/B,C,D Quadrant Clock (Input/Output)

These four pins are the quadrant clock inputs. When not used as a register control signal, these pins can function as general purpose I/O.

#### TCK Test Clock

Clock signal to shift the JTAG data into the device. This pin functions as an I/O when the JTAG fuse is not programmed.

## TDI Test Data In

Serial data input for JTAG instructions and data. Data is shifted in on the rising edge of TCLK. This pin functions as an I/O when the JTAG fuse is not programmed.

#### TDO Test Data Out

Serial data output for JTAG instructions and test data. This pin functions as an I/O when the JTAG fuse is not programmed.

#### TMS Test Mode Select

Serial data input for JTAG test mode. Data is shifted in on the rising edge of TCLK. This pin functions as an I/O when the JTAG fuse is not programmed.

# **Actel MIL-STD-883 Product Flow**

| Step | Screen                                                                                                                                                                                 | 833 Method                                               | 833—Class B<br>Requirement |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------|

| 1.0  | Internal Visual                                                                                                                                                                        | 2010, Test Condition B                                   | 100%                       |

| 2.0  | Temperature Cycling                                                                                                                                                                    | 1010, Test Condition C                                   | 100%                       |

| 3.0  | Constant Acceleration                                                                                                                                                                  | 2001, Test Condition E<br>(min), Y1, Orientation Only    | 100%                       |

| 4.0  | Seal<br>a.Fine<br>b.Gross                                                                                                                                                              | 1014                                                     | 100%<br>100%               |

| 5.0  | Visual Inspection                                                                                                                                                                      | 2009                                                     | 100%                       |

| 6.0  | Pre-burn-in<br>Electrical Parameters                                                                                                                                                   | In accordance with Actel applicable device specification | 100%                       |

| 7.0  | Burn-in Test                                                                                                                                                                           | 1015 Condition D<br>160 hours @ 125°C Min.               | 100%                       |

| 8.0  | Interim (Post-burn-in) Electrical Parameters                                                                                                                                           | In accordance with Actel applicable device specification | 100%                       |

| 9.0  | Percent Defective Allowable                                                                                                                                                            | 5%                                                       | All Lots                   |

| 10.0 | Final Electrical Test                                                                                                                                                                  | In accordance with Actel applicable device specification |                            |

|      | <ul> <li>a. Static Tests</li> <li>(1) 25°C</li> <li>(Subgroup 1, Table I, 5005)</li> <li>(2) -55°C and +125°C</li> <li>(Subgroups 2, 3, Table I, 5005)</li> </ul>                      |                                                          | 100%                       |

|      | <ul> <li>b. Dynamic and Functional Tests</li> <li>(1) 25°C</li> <li>(Subgroup 7, Table I, 5005)</li> <li>(2) -55°C and +125°C</li> <li>(Subgroups 8A and 8B, Table I, 5005)</li> </ul> |                                                          | 100%                       |

|      | c. Switching Tests at 25°C (Subgroup 9, Table I, 5005)                                                                                                                                 |                                                          | 100%                       |

| 11.0 | Qualification or Quality Confirmation Inspection Test Sample Selection (Group A and Group B)                                                                                           | 5005                                                     | All Lots                   |

| 12.0 | External Visual                                                                                                                                                                        | 2009                                                     | 100%                       |

# Actel Extended Flow 1, 2

|     | Screen                                                                                                                      | Method                                                   | Require-<br>ment     |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|

| 1.  | Wafer Lot Acceptance <sup>3</sup>                                                                                           | 5007 with step coverage waiver                           | All Lots             |

| 2.  | Destructive In-Line Bond Pull <sup>4</sup>                                                                                  | 2011, condition D                                        | Sample               |

| 3.  | Internal Visual                                                                                                             | 2010, condition A                                        | 100%                 |

| 4.  | Serialization                                                                                                               |                                                          | 100%                 |

| 5.  | Temperature Cycling                                                                                                         | 1010, condition C                                        | 100%                 |

| 6.  | Constant Acceleration                                                                                                       | 2001, condition E (min), Y <sub>1</sub> orientation only | 100%                 |

| 7.  | Visual Inspection                                                                                                           | 2009                                                     | 100%                 |

| 8.  | Particle Impact Noise Detection                                                                                             | 2020, condition A                                        | 100%                 |

| 9.  | Radiographic                                                                                                                | 2012                                                     | 100%                 |

| 10. | Pre-burn-in Test                                                                                                            | In accordance with Actel applicable device specification | 100%                 |

| 11. | Burn-in Test                                                                                                                | 1015, condition D, 240 hours @ 125°C minimum             | 100%                 |

| 12. | Interim (Post-burn-in) Electrical Parameters                                                                                | In accordance with Actel applicable device specification | 100%                 |

| 13. | Reverse Bias Burn-in                                                                                                        | 1015, condition C, 72 hours @ 150°C minimum              | 100%                 |

| 14. | Interim (Post-burn-in) Electrical Parameters                                                                                | In accordance with Actel applicable device specification | 100%                 |

| 15. | Percent Defective Allowable (PDA) Calculation                                                                               | 5%, 3% functional parameters @ 25°C                      | All Lots             |

| 16. | Final Electrical Test                                                                                                       | In accordance with Actel applicable device specification | 100%                 |

|     | a. Static Tests (1) 25°C (Subgroup 1, Table1) (2) -55°C and +125°C (Subgroups 2, 3, Table 1)                                | 5005<br>5005                                             | 100%                 |

|     | b. Dynamic and Functional Tests (1) 25°C (Subgroup 7, Table 15) (2) -55°C and +125°C (Subgroups 5 and 6, 8a and b, Table 1) | 5005<br>5005                                             | 100%                 |

|     | c. Switching Tests at 25°C<br>(Subgroup 9, Table I, 5005)                                                                   | 5005                                                     | 100%                 |

| 17. | Seal<br>a.Fine<br>b.Gross                                                                                                   | 1014                                                     | 100%                 |

| 18. | Qualification or Quality Conformance<br>Inspection Test Sample Selection                                                    | 5005                                                     | Group A &<br>Group B |

| 19  | External Visual                                                                                                             | 2009                                                     | 100%                 |

- 1. Actel offers the Extended Flow in order to satisfy those customers that require additional screening beyond the requirements of MIL-STD-883, Class B. Actel is compliant to the requirements of MIL-STD-883, Paragraph 1.2.1, and MIL-I-38535, Appendix A. Actel is offering this extended flow incorporating the majority of the screening procedures as outlined in Method 5004 of MIL-STD-883 Class S. The exceptions to Method 5004 are shown in notes 2 to 4 below.

- 2. Method 5004 requires a 100 percent Radiation latch-up testing to Method 1020. Actel will not be performing any radiation testing, and this requirement must be waived in its entirety.

- 3. Wafer lot acceptance is performed to Method 5007; however the step coverage requirement as specified in Method 2018 must be waived.

- 4. Method 5004 requires a 100 percent, nondestructive bond pull to Method 2023. Actel substitutes a destructive bond pull to Method 2011, condition D on a sample basis only.

## Absolute Maximum Ratings<sup>1</sup>

#### Free air temperature range

| Symbol           | Parameter                               | Limits                  | Units |

|------------------|-----------------------------------------|-------------------------|-------|

| V <sub>CC</sub>  | DC Supply Voltage <sup>2, 3, 4</sup>    | -0.5 to +7.0            | V     |

| V <sub>I</sub>   | Input Voltage                           | $-0.5$ to $V_{CC}$ +0.5 | V     |

| V <sub>O</sub>   | Output Voltage                          | $-0.5$ to $V_{CC}$ +0.5 | V     |

| I <sub>IO</sub>  | I/O Source Sink<br>Current <sup>5</sup> | ±20                     | mA    |

| T <sub>STG</sub> | Storage Temperature                     | -65 to +150             | °C    |

#### Notes:

- 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Device should not be operated outside the recommended operating conditions.

- 2. Device inputs are normally high impedance and draw extremely low current. However, when input voltage is greater than  $V_{CC}$  + 0.5 V or less than GND 0.5 V, the internal protection diode will be forward biased and can draw excessive current.

# **Package Thermal Characteristics**

The device junction to case thermal characteristic is  $\theta$ jc, and the junction to ambient air characteristic is  $\theta$ ja. The thermal characteristics for  $\theta$ ja are shown with two different air flow rates.

## **Recommended Operating Conditions**

| Parameter                         | Commercial | Military    | Units            |

|-----------------------------------|------------|-------------|------------------|

| Temperature<br>Range <sup>1</sup> | 0 to +70   | -55 to +125 | °C               |

| Power Supply<br>Tolerance         | ±5         | ±10         | %V <sub>CC</sub> |

#### Note:

1. Ambient temperature  $(T_A)$  is used for commercial and industrial; case temperature  $(T_C)$  is used for military.

Maximum junction temperature is 150°C.

A sample calculation of the absolute maximum power dissipation allowed for a CPGA 176-pin package at military temperature is as follows:

$$\frac{Max.\ junction\ temp.\ (^{\circ}C)-Max.\ military\ temp.}{\theta ja\ (^{\circ}C/W)}\ =\ \frac{150^{\circ}C-125^{\circ}C}{23^{\circ}C/W}\ =\ 1.1\ W$$

| Package Type           | Pin Count | θјс | θja<br>Still Air | θja<br>300 ft/min | Units |

|------------------------|-----------|-----|------------------|-------------------|-------|

| Ceramic Pin Grid Array | 84        | 20  | 33               | 20                | °C/W  |

|                        | 132       | 20  | 26               | 16                | °C/W  |

|                        | 133       | 20  | 37               | 24                | °C/W  |

|                        | 176       | 20  | 23               | 12                | °C/W  |

|                        | 207       | 20  | 22               | 14                | °C/W  |

|                        | 257       | 20  | 21               | 13                | °C/W  |

| Ceramic Quad Flatpack  | 84        | 13  | 40               | 25                | °C/W  |

|                        | 132       | 13  | 55               | 30                | °C/W  |

|                        | 172       | 13  | 25               | 15                | °C/W  |

|                        | 196       | 13  | 36               | 24                | °C/W  |

|                        | 256       | 13  | 30               | 18                | °C/W  |

## **Electrical Specifications**

|                                 |                                        | Commercial                              |      | nmercial              | M    | ilitary               |       |

|---------------------------------|----------------------------------------|-----------------------------------------|------|-----------------------|------|-----------------------|-------|

| Symbol                          | Parameter                              | Test Condition                          | Min. | Max.                  | Min. | Max.                  | Units |

| V <sub>OH</sub> <sup>1, 2</sup> | HIGH Level Output                      | I <sub>OH</sub> = -4 mA (CMOS)          |      | '                     | 3.7  | <u>'</u>              | V     |

|                                 |                                        | $I_{OH} = -6 \text{ mA (CMOS)}$         | 3.84 |                       |      |                       | V     |

| V <sub>OL</sub> <sup>1, 2</sup> | LOW Level Output                       | I <sub>OL</sub> = +6 mA (CMOS)          |      | 0.33                  |      | 0.4                   | V     |

| V <sub>IH</sub>                 | HIGH Level Input                       | TTL Inputs                              | 2.0  | V <sub>CC</sub> + 0.3 | 2.0  | V <sub>CC</sub> + 0.3 | V     |

| V <sub>IL</sub>                 | LOW Level Input                        | TTL Inputs                              | -0.3 | 0.8                   | -0.3 | 0.8                   | V     |

| I <sub>IN</sub>                 | Input Leakage                          | V <sub>I</sub> = V <sub>CC</sub> or GND | -10  | +10                   | -10  | +10                   | μA    |

| I <sub>OZ</sub>                 | 3-state Output Leakage                 | $V_O = V_{CC}$ or GND                   | -10  | +10                   | -10  | +10                   | μA    |

| C <sub>IO</sub>                 | I/O Capacitance <sup>3, 4</sup>        |                                         |      | 10                    |      | 10                    | pF    |

| I <sub>CC(S)</sub>              | Standby V <sub>CC</sub> Supply Current | $V_I = V_{CC}$ or GND, $I_O = 0$ mA     |      |                       |      |                       |       |

|                                 |                                        | ACT 1                                   |      | 3                     |      | 20                    | mA    |

|                                 |                                        | ACT 2/3/1200XL/3200DX                   |      | 2                     |      | 20                    | mA    |

| I <sub>CC(D)</sub>              | Dynamic V <sub>CC</sub> Supply Current | See "Power Dissipation" Sect            | ion  |                       |      |                       |       |

#### Notes:

- 1. Actel devices can drive and receive either CMOS or TTL signal levels. No assignment of I/Os as TTL or CMOS is required.

- 2. Tested one output at a time,  $V_{CC} = min$ .

- 3. Not tested; for information only.

- 4.  $V_{OUT} = 0V$ , f = 1 MHz

## **General Power Equation**

$$P = [I_{CC} standby + I_{CC} active] * V_{CC} + I_{OL} * V_{OL} * N + I_{OH} * (V_{CC} - V_{OH}) * M$$

#### Where:

I<sub>CC</sub>standby is the current flowing when no inputs or outputs are changing.

I<sub>CC</sub>active is the current flowing due to CMOS switching.

I<sub>OL</sub>, I<sub>OH</sub> are TTL sink/source currents.

VOL, VOH are TTL level output voltages.

N equals the number of outputs driving TTL loads to V<sub>OL</sub>.

M equals the number of outputs driving TTL loads to V<sub>OH</sub>

An accurate determination of N and M is problematical because their values depend on the family type, on design details, and on the system I/O. The power can be divided into two components—static and active.

#### Static Power Component

Actel FPGAs have small static power components that result in power dissipation lower than that of PALs or PLDs. By integrating multiple PALs or PLDs into one FPGA, an even greater reduction in board-level power dissipation can be achieved. The power due to standby current is typically a small component of the overall power. Standby power is calculated below for commercial, worst-case conditions.

| Family        | $I_{CC}$ | $V_{CC}$ | Power   |

|---------------|----------|----------|---------|

| ACT 1         | 3 mA     | 5.25 V   | 15.8 mW |

| 1200XL/3200DX | 2mA      | 5.25V    | 10.5mW  |

| ACT 2         | 2 mA     | 5.25 V   | 10.5 mW |

| ACT 3         | 2 mA     | 5.25 V   | 10.5 mW |

The static power dissipated by TTL loads depends on the number of outputs driving high or low and the DC load current. Again, this value is typically small. For instance, a 32-bit bus sinking 4 mA at 0.33 V will generate 42 mW with all outputs driving low, and 140 mW with all outputs driving high.

#### **Active Power Component**

Power dissipation in CMOS devices is usually dominated by the active (dynamic) power dissipation. This component is frequency dependent, a function of the logic and the external I/O. Active power dissipation results from charging internal chip capacitances of the interconnect, unprogrammed antifuses, module inputs, and module outputs, plus external capacitance due to PC board traces and load device inputs. An additional component of the active power dissipation is the totem-pole current in CMOS transistor pairs. The net effect can be associated with an equivalent capacitance that can be combined with frequency and voltage to represent active power dissipation.

### **Equivalent Capacitance**

The power dissipated by a CMOS circuit can be expressed by the Equation 1

Power (uW) =

$$C_{EQ} * V_{CC}^2 * F$$

(1)

where:

C<sub>EQ</sub> is the equivalent capacitance expressed in pF.

$V_{CC}$  is the power supply in volts.

F is the switching frequency in MHz.

Equivalent capacitance is calculated by measuring  $I_{CC}$  active at a specified frequency and voltage for each circuit component of interest. Measurements are made over a range of frequencies at a fixed value of  $V_{CC}$ . Equivalent capacitance is frequency independent so that the results can be used over a wide range of operating conditions. Equivalent capacitance values are shown below.

#### **CEQ Values for Actel FPGAs**

|                                                                                             |       | 1200XL |       |       |

|---------------------------------------------------------------------------------------------|-------|--------|-------|-------|

|                                                                                             | ACT 1 | 3200DX | ACT 2 | ACT 3 |

| Modules (C <sub>EQM</sub> )                                                                 | 3.7   | 5.2    | 5.8   | 6.7   |

| Input Buffers (C <sub>EQI</sub> )                                                           | 22.1  | 11.6   | 12.9  | 7.2   |

| Output Buffers (C <sub>EQO</sub> )                                                          | 31.2  | 23.8   | 23.8  | 10.4  |

| Routed Array Clock<br>Buffer Loads (C <sub>EQCR</sub> )                                     | 4.6   | 3.5    | 3.9   | 1.6   |

| $\begin{array}{c} \textbf{Dedicated Clock Buffer} \\ \textbf{Loads (C}_{EQCD}) \end{array}$ | n/a   | n/a    | n/a   | 0.7   |

| I/O Clock Buffer Loads (C <sub>EQCI</sub> )                                                 | n/a   | n/a    | n/a   | 0.9   |

To calculate the active power dissipated from the complete design, the switching frequency of each part of the logic must be known. Equation 2 shows a piecewise linear summation over all components, it applies to all ACT 1, 1200XL, ACT 2, and ACT 3 devices. Since the ACT 1 family has only one routed array clock, the terms labeled routed\_Clk2, dedicated\_Clk, and IO\_Clk do not apply. Similarly, the ACT 2 family has two routed array clocks, and the dedicated\_Clk and IO\_Clk terms do not apply. For ACT 3 devices, all terms will apply.

$$\begin{split} &Power = {V_{CC}}^2*\left[ (m*C_{EQM}*f_m)_{modules} + (n*C_{EQI}*f_n)_{inputs} + \\ & (p*(C_{EQO}+C_L)*f_p)_{outputs} + 0.5*(q_1*C_{EQCR}*f_{q1})_{routed\_Clk1} + \\ & + (r_1*f_{q1})_{routed\_Clk1} + 0.5*(q_2*C_{EQCR}*f_{q2})_{routed\_Clk2} + \\ & + (r_2*f_{q2})_{routed\_Clk2} + 0.5*(s_1*C_{EQCD}*f_{s1})_{dedicated\_Clk} + \\ & (s_2*C_{EQCI}*f_{s2})_{10-Clk} \right] \end{split}$$

where:

m = Number of logic modules switching at fm

n = Number of input buffers switching at fn

p = Number of output buffers switching at fp

q<sub>1</sub> = Number of clock loads on the first routed array clock (all families)

q<sub>2</sub> = Number of clock loads on the second routed array clock (ACT 2, 1200XL, ACT 3 only)

r<sub>1</sub> = Fixed capacitance due to first routed array clock (all families)

r<sub>2</sub> = Fixed capacitance due to second routed array clock (ACT 2, 1200XL, ACT 3 only)

s<sub>1</sub> = Fixed number of clock loads on the dedicated array clock (ACT 3 only)

s<sub>2</sub> = Fixed number of clock loads on the dedicated I/O clock (ACT 3 only)

$C_{EOM}$  = Equivalent capacitance of logic modules in pF

$C_{EQI}$  = Equivalent capacitance of input buffers in pF

C<sub>EQ0</sub> = Equivalent capacitance of output buffers in pF

C<sub>EQCR</sub> = Equivalent capacitance of routed array clock in nF

C<sub>EQCD</sub> = Equivalent capacitance of dedicated array clock in pF

$C_{EQCI}$  = Equivalent capacitance of dedicated I/O clock in pF

$C_L$  = Output lead capacitance in pF

$f_m$  = Average logic module switching rate in MHz

$f_n$  = Average input buffer switching rate in MHz

$f_p$  = Average output buffer switching rate in MHz

f<sub>q1</sub> = Average first routed array clock rate in MHz (all families)

$f_{q2}$  = Average second routed array clock rate in MHz (ACT 2, 1200XL, ACT 3 only)

f<sub>s1</sub> = Average dedicated array clock rate in MHz (ACT 3 only)

f<sub>s2</sub> = Average dedicated I/O clock rate in MHz (ACT 3 only)

# Fixed Capacitance Values for Actel FPGAs (pF)

#### $\begin{matrix} r_1 \\ routed\_Clk1 \end{matrix}$ $\begin{matrix} r_2 \\ routed\_Clk2 \end{matrix}$ **Device Type** A1010B 41 n/a A1020B 69 n/a A1240A 134 134 A1280A 168 168 A1280XL 168 168 A1425A 75 75 A1460A 165 165 A14100A 195 195 A32100DX 178 178 A32200DX 230 230

## Fixed Clock Loads ( $s_1/s_2$ —ACT 3 Only)

|             | $s_1$          | $s_2$          |

|-------------|----------------|----------------|

|             | Clock Loads on | Clock Loads on |

|             | Dedicated      | Dedicated      |

| Device Type | Array Clock    | I/O Clock      |

| A1425A      | 160            | 100            |

| A1460A      | 432            | 168            |

| A14100A     | 697            | 228            |

|             |                |                |

# **Determining Average Switching Frequency**

To determine the switching frequency for a design, you must have a detailed understanding of the data values input to the circuit. The guidelines in the table below are meant to represent worst-case scenarios so that they can be generally used to predict the upper limits of power dissipation.

| Туре                                                  | ACT 1          | ACT 2/1200XL/3200DX       | ACT 3                     |

|-------------------------------------------------------|----------------|---------------------------|---------------------------|

| Logic modules (m)                                     | 90% of modules | 80% of modules            | 80% of modules            |

| Input switching (n)                                   | # inputs/4     | # inputs/4                | # inputs/4                |

| Outputs switching (p)                                 | #outputs/4     | #outputs/4                | #outputs/4                |

| First routed array clock loads (q <sub>1</sub> )      | 40% of modules | 40% of sequential modules | 40% of sequential modules |

| Second routed array clock loads (q <sub>2</sub> )     | n/a            | 40% of sequential modules | 40% of sequential modules |

| Load capacitance (C <sub>L</sub> )                    | 35 pF          | 35 pF                     | 35 pF                     |

| Average logic module switching rate (f <sub>m</sub> ) | F/10           | F/10                      | F/10                      |

| Average input switching rate (f <sub>n</sub> )        | F/5            | F/5                       | F/5                       |

| Average output switching rate (f <sub>p</sub> )       | F/10           | F/10                      | F/10                      |

| Average first routed array clock rate (fq1)           | F              | F                         | F/2                       |

| Average second routed array clock rate $(f_{q2})$     | n/a            | F/2                       | F/2                       |

| Average dedicated array clock rate (f <sub>s1</sub> ) | n/a            | n/a                       | F                         |

| Average dedicated I/O clock rate (f <sub>s2</sub> )   | n/a            | n/a                       | F                         |

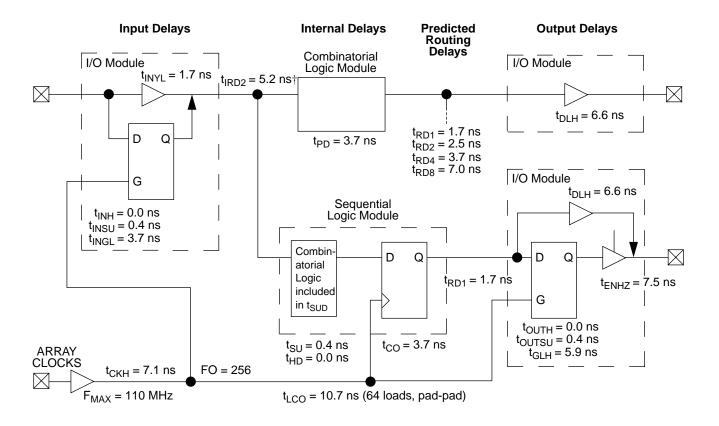

## 1200XL Timing Model\*

\*Values shown for A1280XL-1 at worst-case military conditions.

† Input Module Predicted Routing Delay

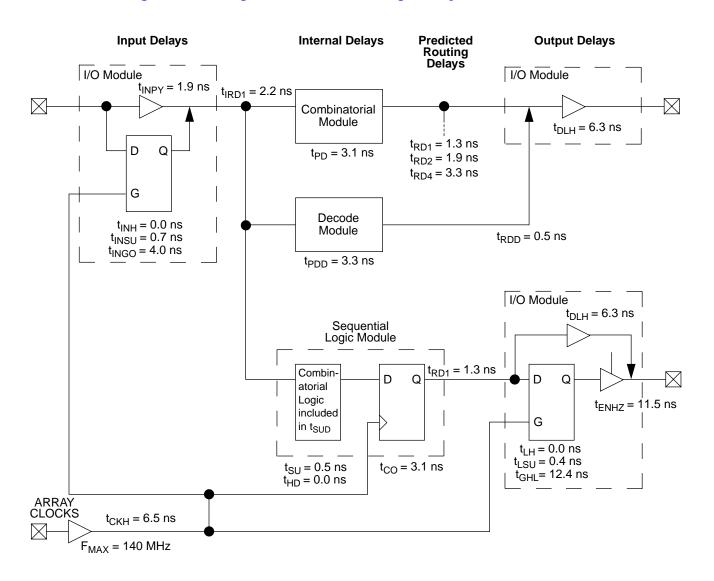

## 3200DX Timing Model (Logic Functions using Array Clocks)\*

<sup>\*</sup>Values shown for A32100DX-1 at worst-case military conditions.

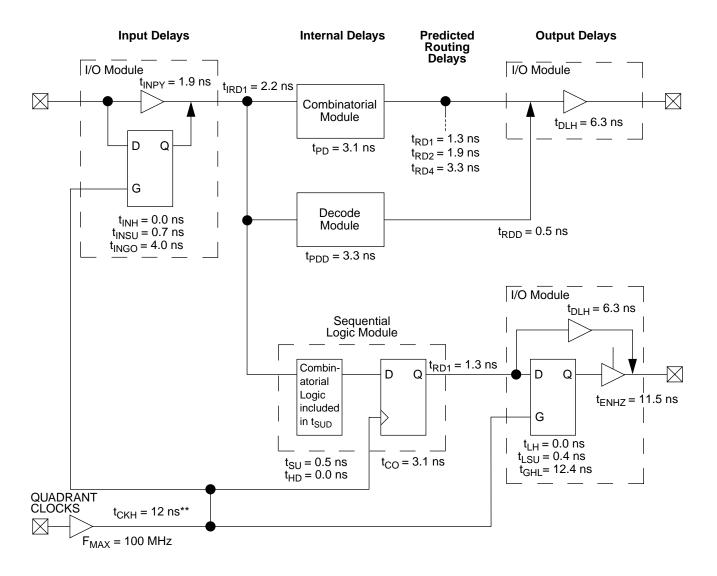

## 3200DX Timing Model (Logic Functions using Quadrant Clocks)\*

<sup>\*</sup> Values shown for A32100DX-1 at worst-case military conditions.

<sup>\*\*</sup> Load dependent.

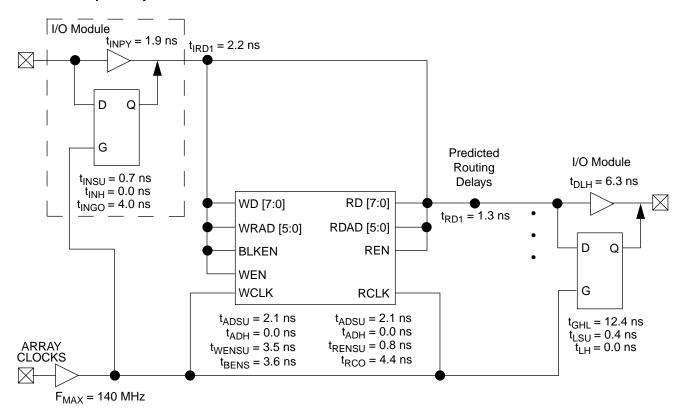

## 3200DX Timing Model (SRAM Functions)\*

## **Input Delays**

<sup>\*</sup>Values shown for A32100DX-1 at worst-case military conditions.

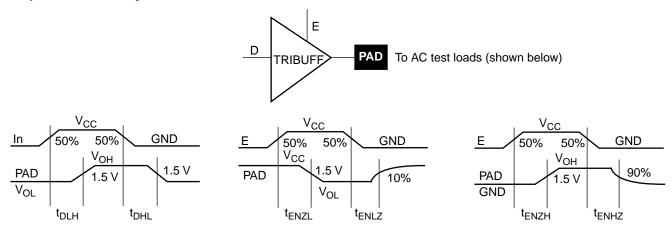

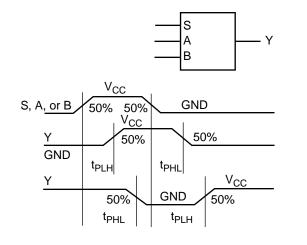

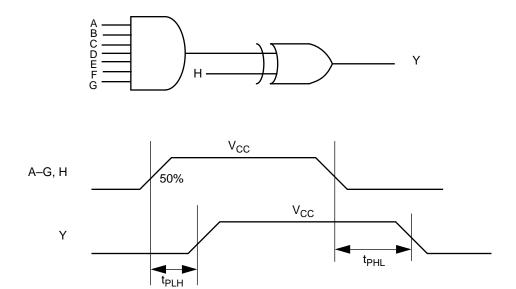

#### **Parameter Measurement**

#### **Output Buffer Delays**

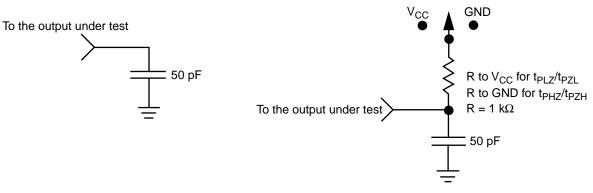

#### **AC Test Load**

Load 1 (Used to measure propagation delay)

Load 2 (Used to measure rising/falling edges)

## **Combinatorial Macro Delays**

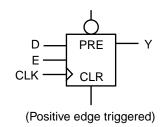

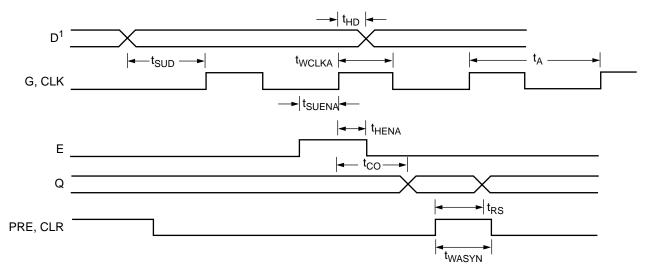

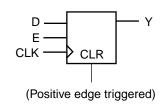

# **Sequential Timing Characteristics**

Flip-Flops and Latches (ACT 1, ACT 2, and 1200XL/3200DX)

#### Note:

1. D represents all data functions involving A, B, and S for multiplexed flip-flops.

# **Sequential Timing Characteristics (continued)**

## Flip-Flops and Latches (ACT 3)

#### Note:

1. D represents all data functions involving A, B, and S for multiplexed flip-flops.

# **Sequential Timing Characteristics (continued)**

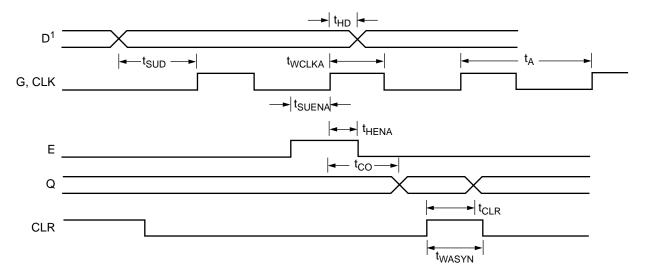

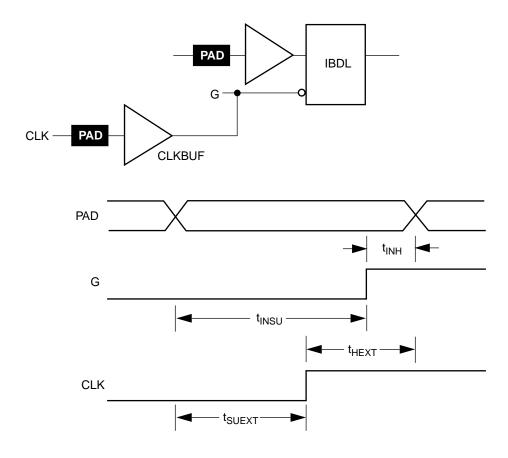

# Input Buffer Latches (ACT 2 and 1200XL/3200DX)

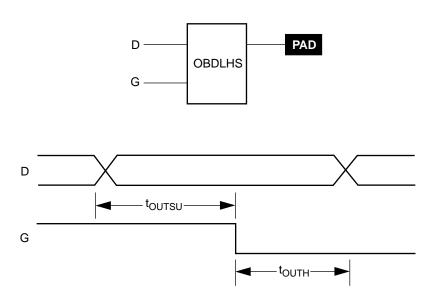

## Output Buffer Latches (ACT 2 and 1200XL/3200DX)

# **Decode Module Timing**

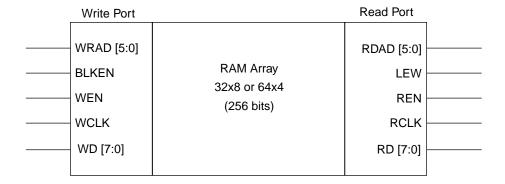

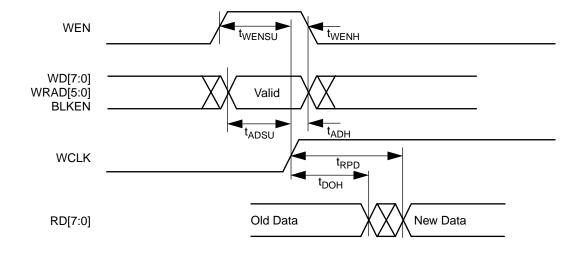

# **SRAM Timing Characteristics**

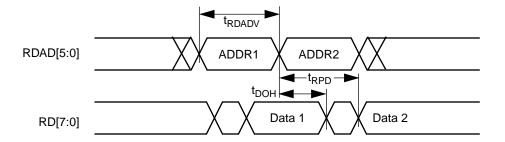

## **Dual-Port SRAM Timing Waveforms**

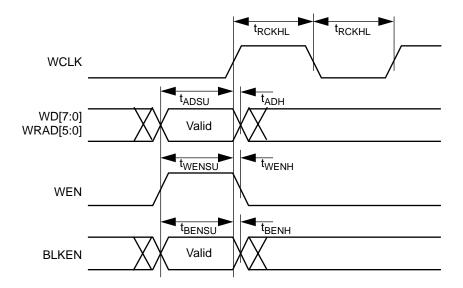

## 3200DX SRAM Write Operation

**Note:** Identical timing for falling-edge clock.

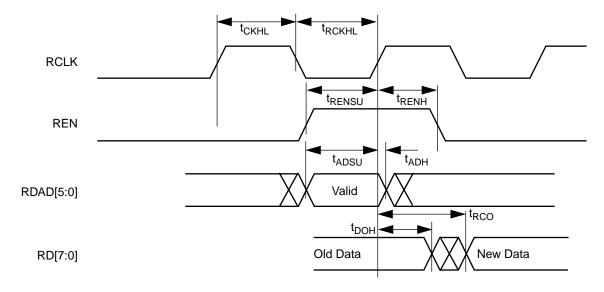

## 3200DX SRAM Synchronous Read Operation

Note: Identical timing for falling-edge clock.

## 3200DX SRAM Asynchronous Read Operation—Type 1

## (Read Address Controlled)

## 3200DX SRAM Asynchronous Read Operation—Type 2

## (Write Address Controlled)

## **ACT 1 Timing Characteristics**

## (Worst-Case Military Conditions)

| Logic Module       | Propagation Delays                         | −1 S | -1 Speed |      | Std Speed |       |

|--------------------|--------------------------------------------|------|----------|------|-----------|-------|

| Parameter          | Description                                | Min. | Max.     | Min. | Max.      | Units |

| t <sub>PD1</sub>   | Single Module                              |      | 4.7      |      | 5.5       | ns    |

| t <sub>PD2</sub>   | Dual Module Macros                         |      | 10.8     |      | 12.7      | ns    |

| $t_{CO}$           | Sequential Clk to Q                        |      | 4.7      |      | 5.5       | ns    |

| $t_{GO}$           | Latch G to Q                               |      | 4.7      |      | 5.5       | ns    |

| t <sub>RS</sub>    | Flip-Flop (Latch) Reset to Q               |      | 4.7      |      | 5.5       | ns    |

| Predicted Ro       | uting Delays <sup>1</sup>                  |      |          |      |           |       |

| t <sub>RD1</sub>   | FO=1 Routing Delay                         |      | 1.5      |      | 1.7       | ns    |

| t <sub>RD2</sub>   | FO=2 Routing Delay                         |      | 2.3      |      | 2.7       | ns    |

| t <sub>RD3</sub>   | FO=3 Routing Delay                         |      | 3.4      |      | 4.0       | ns    |

| t <sub>RD4</sub>   | FO=4 Routing Delay                         |      | 5.0      |      | 5.9       | ns    |

| t <sub>RD8</sub>   | FO=8 Routing Delay                         |      | 10.6     |      | 12.5      | ns    |

| Sequential Tir     | ming Characteristics <sup>2</sup>          |      |          |      |           |       |

| t <sub>SUD</sub>   | Flip-Flop (Latch) Data Input Setup         | 8.8  |          | 10.4 |           | ns    |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data Input Hold          | 0.0  |          | 0.0  |           | ns    |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Setup             | 8.8  |          | 10.4 |           | ns    |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold              | 0.0  |          | 0.0  |           | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch) Clock Active Pulse Width | 10.9 |          | 12.9 |           | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch) Asynchronous Pulse Width | 10.9 |          | 12.9 |           | ns    |

| t <sub>A</sub>     | Flip-Flop Clock Input Period               | 23.2 |          | 27.3 |           | ns    |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Clock<br>Frequency       |      | 44       |      | 37        | MHz   |

<sup>1.</sup> Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

<sup>2.</sup> Setup times assume fanout of 3. Further derating information can be obtained from the DirectTime Analyzer utility.

# **ACT 1 Timing Characteristics (continued)**

## (Worst-Case Military Conditions)

| Input Module Propagation Delays |                                         | –1 S                | -1 Speed     |              | Speed        |              |       |

|---------------------------------|-----------------------------------------|---------------------|--------------|--------------|--------------|--------------|-------|

| Parameter                       | Description                             |                     | Min.         | Max.         | Min.         | Max.         | Units |

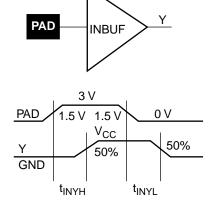

| t <sub>INYH</sub>               | Pad to Y High                           |                     |              | 4.9          |              | 5.8          | ns    |

| t <sub>INYL</sub>               | Pad to Y Low                            |                     |              | 4.9          |              | 5.8          | ns    |

| Input Modul                     | e Predicted Routing Delays <sup>1</sup> |                     |              |              |              |              |       |

| t <sub>IRD1</sub>               | FO=1 Routing Delay                      |                     |              | 1.5          |              | 1.7          | ns    |

| t <sub>IRD2</sub>               | FO=2 Routing Delay                      |                     |              | 2.3          |              | 2.7          | ns    |

| t <sub>IRD3</sub>               | FO=3 Routing Delay                      |                     |              | 3.4          |              | 4.0          | ns    |

| t <sub>IRD4</sub>               | FO=4 Routing Delay                      |                     |              | 5.0          |              | 5.9          | ns    |

| t <sub>IRD8</sub>               | FO=8 Routing Delay                      |                     |              | 10.6         |              | 12.5         | ns    |

| Global Clock                    | k Network                               |                     |              |              |              |              |       |

| t <sub>CKH</sub>                | Input Low to High                       | FO = 16<br>FO = 128 |              | 7.8<br>8.9   |              | 9.2<br>10.5  | ns    |

| t <sub>CKL</sub>                | Input High to Low                       | FO = 16<br>FO = 128 |              | 10.3<br>11.2 |              | 12.1<br>13.2 | ns    |

| t <sub>PWH</sub>                | Minimum Pulse Width High                | FO = 16<br>FO = 128 | 10.4<br>10.9 |              | 12.2<br>12.9 |              | ns    |

| t <sub>PWL</sub>                | Minimum Pulse Width Low                 | FO = 16<br>FO = 128 | 10.4<br>10.9 |              | 12.2<br>12.9 |              | ns    |

| t <sub>CKSW</sub>               | Maximum Skew                            | FO = 16<br>FO = 128 |              | 1.9<br>2.9   |              | 2.2<br>3.4   | ns    |

| t <sub>P</sub>                  | Minimum Period                          | FO = 16<br>FO = 128 | 21.7<br>23.2 |              | 25.6<br>27.3 |              | ns    |

| f <sub>MAX</sub>                | Maximum Frequency                       | FO = 16<br>FO = 128 |              | 46<br>44     |              | 40<br>37     | MHz   |

<sup>1.</sup> These parameters should be used for estimating device performance. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

# **ACT 1 Timing Characteristics (continued)**

# (Worst-Case Military Conditions)

| Output Mod        | Output Module Timing          |      | -1 Speed |      | Std Speed |       |

|-------------------|-------------------------------|------|----------|------|-----------|-------|

| Parameter         | Description                   | Min. | Max.     | Min. | Max.      | Units |

| TTL Output        | Module Timing <sup>1</sup>    |      |          |      |           |       |

| t <sub>DLH</sub>  | Data to Pad High              |      | 12.1     |      | 14.2      | ns    |

| t <sub>DHL</sub>  | Data to Pad Low               |      | 13.8     |      | 16.3      | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to High          |      | 12.0     |      | 14.1      | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to Low           |      | 14.6     |      | 17.1      | ns    |

| t <sub>ENHZ</sub> | Enable Pad High to Z          |      | 16.0     |      | 18.8      | ns    |

| t <sub>ENLZ</sub> | Enable Pad Low to Z           |      | 14.5     |      | 17.0      | ns    |

| d <sub>TLH</sub>  | Delta Low to High             |      | 0.09     |      | 0.11      | ns/pF |

| d <sub>THL</sub>  | Delta High to Low             |      | 0.12     |      | 0.15      | ns/pF |

| CMOS Outp         | ut Module Timing <sup>1</sup> |      |          |      |           |       |

| t <sub>DLH</sub>  | Data to Pad High              |      | 15.1     |      | 17.7      | ns    |

| t <sub>DHL</sub>  | Data to Pad Low               |      | 11.5     |      | 13.6      | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to High          |      | 12.0     |      | 14.1      | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to Low           |      | 14.6     |      | 17.1      | ns    |

| t <sub>ENHZ</sub> | Enable Pad High to Z          |      | 16.0     |      | 18.8      | ns    |

| t <sub>ENLZ</sub> | Enable Pad Low to Z           |      | 14.5     |      | 17.0      | ns    |

| d <sub>TLH</sub>  | Delta Low to High             |      | 0.16     |      | 0.18      | ns/pF |

| d <sub>THL</sub>  | Delta High to Low             |      | 0.09     |      | 0.11      | ns/pF |

<sup>1.</sup> Delays based on 50 pF loading.

<sup>2.</sup> SSO information can be found in the "Simultaneously Switching Output Limits for Actel FPGAs" application note.

#### **A1240A Timing Characteristics**

## (Worst-Case Military Conditions)

| Logic Module       | Propagation Delays <sup>1</sup>            | -1 S | peed | Std S | Speed |       |

|--------------------|--------------------------------------------|------|------|-------|-------|-------|

| Parameter          | Description                                | Min. | Max. | Min.  | Max.  | Units |

| t <sub>PD1</sub>   | Single Module                              |      | 5.2  |       | 6.1   | ns    |

| $t_{CO}$           | Sequential Clk to Q                        |      | 5.2  |       | 6.1   | ns    |

| $t_{GO}$           | Latch G to Q                               |      | 5.2  |       | 6.1   | ns    |

| t <sub>RS</sub>    | Flip-Flop (Latch) Reset to Q               |      | 5.2  |       | 6.1   | ns    |

| Predicted Ro       | uting Delays <sup>2</sup>                  |      |      |       |       |       |

| t <sub>RD1</sub>   | FO=1 Routing Delay                         |      | 1.9  |       | 2.2   | ns    |

| t <sub>RD2</sub>   | FO=2 Routing Delay                         |      | 2.4  |       | 2.8   | ns    |

| t <sub>RD3</sub>   | FO=3 Routing Delay                         |      | 3.1  |       | 3.7   | ns    |

| t <sub>RD4</sub>   | FO=4 Routing Delay                         |      | 4.3  |       | 5.0   | ns    |

| t <sub>RD8</sub>   | FO=8 Routing Delay                         |      | 6.6  |       | 7.7   | ns    |

| Sequential Tir     | ming Characteristics <sup>3, 4</sup>       |      |      |       |       |       |

| t <sub>SUD</sub>   | Flip-Flop (Latch) Data Input Setup         | 0.5  |      | 0.5   |       | ns    |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data Input Hold          | 0.0  |      | 0.0   |       | ns    |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Setup             | 1.3  |      | 1.3   |       | ns    |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold              | 0.0  |      | 0.0   |       | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch) Clock Active Pulse Width | 7.4  |      | 8.1   |       | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch) Asynchronous Pulse Width | 7.4  |      | 8.1   |       | ns    |

| $t_A$              | Flip-Flop Clock Input Period               | 14.8 |      | 18.6  |       | ns    |

| t <sub>INH</sub>   | Input Buffer Latch Hold                    | 2.5  |      | 2.5   |       | ns    |

| t <sub>INSU</sub>  | Input Buffer Latch Setup                   | -3.5 |      | -3.5  |       | ns    |

| t <sub>OUTH</sub>  | Output Buffer Latch Hold                   | 0.0  |      | 0.0   |       | ns    |

| toutsu             | Output Buffer Latch Setup                  | 0.5  |      | 0.5   |       | ns    |

| $f_{MAX}$          | Flip-Flop (Latch) Clock<br>Frequency       |      | 63   |       | 54    | MHz   |

- 1. For dual-module macros, use  $t_{PD1} + t_{RD1} + t_{PDn}$ ,  $t_{CO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

- 2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

- 3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the DirectTime Analyzer utility.

- 4. Setup and hold timing parameters for the Input Buffer Latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G input subtracts (adds) to the internal setup (hold) time.

## **A1240A Timing Characteristics (continued)**

## (Worst-Case Military Conditions)

| Input Module Propagation Delays |                                          | -1 S                | -1 Speed     |              | Speed        |              |       |

|---------------------------------|------------------------------------------|---------------------|--------------|--------------|--------------|--------------|-------|

| Parameter                       | Description                              |                     | Min.         | Max.         | Min.         | Max.         | Units |

| t <sub>INYH</sub>               | Pad to Y High                            |                     |              | 4.0          |              | 4.7          | ns    |

| t <sub>INYL</sub>               | Pad to Y Low                             |                     |              | 3.6          |              | 4.3          | ns    |

| t <sub>INGH</sub>               | G to Y High                              |                     |              | 6.9          |              | 8.1          | ns    |

| t <sub>INGL</sub>               | G to Y Low                               |                     |              | 6.6          |              | 7.7          | ns    |

| Input Modu                      | le Predicted Routing Delays <sup>1</sup> |                     |              |              |              |              |       |

| t <sub>IRD1</sub>               | FO=1 Routing Delay                       |                     |              | 5.8          |              | 6.9          | ns    |

| t <sub>IRD2</sub>               | FO=2 Routing Delay                       |                     |              | 6.7          |              | 7.8          | ns    |

| t <sub>IRD3</sub>               | FO=3 Routing Delay                       |                     |              | 7.5          |              | 8.8          | ns    |

| t <sub>IRD4</sub>               | FO=4 Routing Delay                       |                     |              | 8.2          |              | 9.7          | ns    |

| t <sub>IRD8</sub>               | FO=8 Routing Delay                       |                     |              | 10.9         |              | 12.9         | ns    |

| Global Cloc                     | k Network                                |                     |              |              |              |              |       |

| t <sub>CKH</sub>                | Input Low to High                        | FO = 32<br>FO = 256 |              | 13.3<br>16.3 |              | 15.7<br>19.2 | ns    |

| t <sub>CKL</sub>                | Input High to Low                        | FO = 32<br>FO = 256 |              | 13.3<br>16.5 |              | 15.7<br>19.5 | ns    |

| t <sub>PWH</sub>                | Minimum Pulse Width High                 | FO = 32<br>FO = 256 | 5.7<br>6.0   |              | 6.7<br>7.1   |              | ns    |

| t <sub>PWL</sub>                | Minimum Pulse Width Low                  | FO = 32<br>FO = 256 | 5.7<br>6.0   |              | 6.7<br>7.1   |              | ns    |

| t <sub>CKSW</sub>               | Maximum Skew                             | FO = 32<br>FO = 256 |              | 0.6<br>3.1   |              | 0.6<br>3.1   | ns    |

| t <sub>SUEXT</sub>              | Input Latch External Setup               | FO = 32<br>FO = 256 | 0.0<br>0.0   |              | 0.0<br>0.0   |              | ns    |

| t <sub>HEXT</sub>               | Input Latch External Hold                | FO = 32<br>FO = 256 | 8.6<br>13.8  |              | 8.6<br>13.8  |              | ns    |

| t <sub>P</sub>                  | Minimum Period                           | FO = 32<br>FO = 256 | 11.5<br>12.2 |              | 13.5<br>14.3 |              | ns    |

| $f_{MAX}$                       | Maximum Frequency                        | FO = 32<br>FO = 256 |              | 87<br>82     |              | 74<br>70     | MHz   |

<sup>1.</sup> These parameters should be used for estimating device performance. Optimization techniques may further reduce delays by 0 to 4 ns. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

# **A1240A Timing Characteristics (continued)**

# (Worst-Case Military Conditions)

| Output Module Timing |                               | -1 S | -1 Speed |      | Std Speed |       |

|----------------------|-------------------------------|------|----------|------|-----------|-------|

| Parameter            | Description                   | Min. | Max.     | Min. | Max.      | Units |

| TTL Output           | Module Timing <sup>1</sup>    |      |          |      |           |       |

| t <sub>DLH</sub>     | Data to Pad High              |      | 11.0     |      | 13.0      | ns    |

| t <sub>DHL</sub>     | Data to Pad Low               |      | 13.9     |      | 16.4      | ns    |

| t <sub>ENZH</sub>    | Enable Pad Z to High          |      | 12.3     |      | 14.4      | ns    |

| t <sub>ENZL</sub>    | Enable Pad Z to Low           |      | 16.1     |      | 19.0      | ns    |

| $t_{ENHZ}$           | Enable Pad High to Z          |      | 9.8      |      | 11.5      | ns    |

| $t_{ENLZ}$           | Enable Pad Low to Z           |      | 11.5     |      | 13.6      | ns    |

| t <sub>GLH</sub>     | G to Pad High                 |      | 12.4     |      | 14.6      | ns    |

| $t_{GHL}$            | G to Pad Low                  |      | 15.5     |      | 18.2      | ns    |

| $d_{TLH}$            | Delta Low to High             |      | 0.09     |      | 0.11      | ns/pF |

| $d_THL$              | Delta High to Low             |      | 0.17     |      | 0.20      | ns/pF |

| CMOS Outp            | ut Module Timing <sup>1</sup> |      |          |      |           |       |

| t <sub>DLH</sub>     | Data to Pad High              |      | 14.0     |      | 16.5      | ns    |

| t <sub>DHL</sub>     | Data to Pad Low               |      | 11.7     |      | 13.7      | ns    |

| t <sub>ENZH</sub>    | Enable Pad Z to High          |      | 12.3     |      | 14.4      | ns    |

| t <sub>ENZL</sub>    | Enable Pad Z to Low           |      | 16.1     |      | 19.0      | ns    |

| t <sub>ENHZ</sub>    | Enable Pad High to Z          |      | 9.8      |      | 11.5      | ns    |

| t <sub>ENLZ</sub>    | Enable Pad Low to Z           |      | 11.5     |      | 13.6      | ns    |

| t <sub>GLH</sub>     | G to Pad High                 |      | 12.4     |      | 14.6      | ns    |

| t <sub>GHL</sub>     | G to Pad Low                  |      | 15.5     |      | 18.2      | ns    |

| $d_{TLH}$            | Delta Low to High             |      | 0.17     |      | 0.20      | ns/pF |

| $d_THL$              | Delta High to Low             |      | 0.12     |      | 0.15      | ns/pF |

<sup>1.</sup> Delays based on 50 pF loading.

<sup>2.</sup> SSO information can be found in the "Simultaneously Switching Output Limits for Actel FPGAs" application note.

#### **A1280A Timing Characteristics**

#### (Worst-Case Military Conditions)

| Logic Module Propagation Delays <sup>1</sup> |                                               | -1 Speed  |     | Std Speed |      |       |  |

|----------------------------------------------|-----------------------------------------------|-----------|-----|-----------|------|-------|--|

| Parameter                                    | Description                                   | Min. Max. |     | Min.      | Max. | Units |  |

| t <sub>PD1</sub>                             | Single Module                                 |           | 5.2 |           | 6.1  | ns    |  |

| $t_{CO}$                                     | Sequential Clk to Q                           |           | 5.2 |           | 6.1  | ns    |  |

| $t_{GO}$                                     | Latch G to Q                                  |           | 5.2 |           | 6.1  | ns    |  |

| $t_{RS}$                                     | Flip-Flop (Latch) Reset to Q                  |           | 5.2 |           | 6.1  | ns    |  |