# Radiation-Hardened Field Programmable Gate Arrays

### **Features**

- Guaranteed Total Dose Radiation Capability

- Low Single Event Upset Susceptibility

- High Dose Rate Survivability

- Latch-Up Immunity Guaranteed

- QML Qualified Devices

- Commercial Devices Available for Prototyping and Pre-Production Requirements

- Gate Capacities of 2,000 and 8,000 Gate Array Gates

- More Design Flexibility than Custom ASICs

- Significantly Greater Densities than Discrete Logic Devices

- Replaces up to 200 TTL Packages

- · Design Library with over 500 Macro Functions

- Single-Module Sequential Functions

- Wide-Input Combinatorial Functions

- · Up to Two High-Speed, Low-Skew Clock Networks

- Two In-Circuit Diagnostic Probe Pins Support Speed Analysis to 50 MHz

- Non-Volatile, User Programmable Devices

- Fabricated in 0.8 Micron Epitaxial Bulk CMOS Process

### **Product Family Profile**

| Device                         | RH1020  | RH1280  |

|--------------------------------|---------|---------|

| Capacity                       |         |         |

| Gate Array Equivalent Gates    | 2,000   | 8,000   |

| PLD Equivalent Gates           | 6,000   | 20,000  |

| TTL Equivalent Packages        | 50      | 200     |

| 20-Pin PAL Equivalent Packages | 20      | 80      |

| Logic Modules                  | 547     | 1,232   |

| C-Modules                      | 547     | 608     |

| S-Modules                      | 0       | 624     |

| Flip-Flops (Maximum)           | 273     | 998     |

| Routing Resources              |         |         |

| Horizontal Tracks/Channel      | 22      | 35      |

| Vertical Tracks/Channel        | 13      | 15      |

| PLICE Antifuse Elements        | 186,000 | 750,000 |

| User I/Os                      | 69      | 140     |

| Packages (by Pin Count)        |         |         |

| Ceramic Quad Flat Pack (CQFP)  | 84      | 172     |

|                                |         |         |

### Description

Actel Corporation, the leader in antifuse-based field programmable gate arrays (FPGAs), introduces fully guaranteed RadHard versions of the popular A1280 and A1020 devices with gate densities of 8,000 and 2,000 gate array gates, respectively.

The RH1280 and RH1020 devices are processed in 0.8 micron, two-level metal epitaxial bulk CMOS technology. The devices are based on Actel's patented channeled array architecture, and employ Actel's PLICE antifuse technology. This revolutionary architecture offers gate array flexibility, high performance, and fast design implementation through user programming.

Actel devices also provide unique on-chip diagnostic probe capabilities, allowing convenient testing and debugging. On-chip clock drivers with hard-wired distribution networks provide efficient clock distribution with minimum skew. A security fuse may be programmed to disable all further programming, and to protect the design from being copied or reverse engineered.

The RH1280 and RH1020 will be available as fully qualified QML devices. Unlike traditional ASIC devices, the design does not have to be finalized six months in advance of receiving the devices. Customers can make design modifications and program new devices within hours. These devices will be fabricated, assembled, and tested at the Lockheed-Martin Federal Systems facility in Manassas, Virginia on an optimized radiation-hardened CMOS process.

### **Radiation Survivability**

In addition to all electrical limits, all radiation characteristics will be tested and guaranteed, reducing overall system-level risks. With total dose hardness of 300K rad(Si), latch-up immunity, and a tested single event upset (SEU) of less than  $1 \times 10^{-6}$  errors/bit-day, these are the only RadHard, high-density field programmable products available today.

### **QML Qualification**

Lockheed Martin Federal Systems in Manassas, Virginia has achieved full QML certification, assuring that quality management, procedures, processes, and controls are in place from wafer fabrication through final test. QML qualification means that quality is built into the production process rather than verified at the end of the line by expensive destructive testing. QML also ensures continuous process improvement, a focus on enhanced quality and reliability, and shortened product introduction and cycle time.

Actel Corporation has achieved transitional QML certification and will be pursuing full QML certification within the next two years. All RH1280 and RH1020 devices will be shipped with a "QML" marking, signifying that the devices and processes have been reviewed and approved by DESC for QML status.

### Designer Series Development Systems

The RH1280 and RH1020 are supported by Actel's Designer Series software, allowing logic design implementation with minimum effort. The Designer Series offers Microsoft Windows and X-Windows graphical user interfaces, and integrates with the resident CAE system to provide a complete design environment: schematic capture, simulation, fully automatic place and route, timing verification, and device programming.

Designer Series also includes the ACTmap VHDL Synthesis and FPGA Optimization tool, and the ACTgen macro builder, a powerful macro function generator for counters, adders, and other complex structural blocks. Designer Series is supported on 386, 486, and Pentium PCs, as well as Sun and H-P workstations. CAE interfaces are provided to the following design environments: Cadence, Viewlogic, Mentor Graphics, and OrCAD.

With the Designer Series software, users can simulate timing over worst-case process, voltage, and temperature ranges. With the RadHard devices, the user can also simulate at two total dose irradiations, 0 KRAD and 300 KRAD.

### **Applications**

The RH1280 and RH1020 devices are targeted for use in military and space applications subject to radiation effects.

1. Accumulated Total Dose Effects

With the significant increase in Earth-orbiting satellite launches and the ever-decreasing time-to-launch design cycles, the RH1280 and RH1020 devices offer the best combination of total dose radiation hardness and quick design implementation necessary for this increasingly competitive industry. In addition, the high total dose capability allows the use of these devices for deep space probes, which encounter other planetary bodies where the total dose radiation effects are more pronounced.

2. Single Event Effects (SEE)

Many space applications are more concerned with the number of single event upsets and potential for latch-up in space. The RH1280 and RH1020 devices are latch-up immune, guaranteeing that no latch-up failures will occur. Single event upsets can occur in these devices as with all semiconductor products, but the rate of upset is low as shown in the RadHard specifications.

3. High Dose Rate Survivability

An additional radiation concern is high dose rate survivability. Solar flares and sudden nuclear events can cause immediate high levels of radiation. The RadHard devices are appropriate for use in these types of applications, including missile systems, ground-based communication systems, and orbiting satellites.

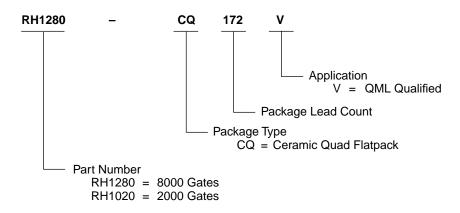

# **Ordering Information**

### **Device Resources**

|        | CQFP 84-pin | CQFP 172-pin |

|--------|-------------|--------------|

| RH1020 | 69          | _            |

| RH1280 | _           | 140          |

### **Pin Description**

### CLKA Clock A (Input)

TTL clock input for clock distribution networks. The clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

### CLKB Clock B (Input)

TTL clock input for clock distribution networks. The clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

### DCLK Diagnostic Clock (Input)

TTL clock input for diagnostic probe and device programming. DCLK is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

### GND Ground

LOW supply voltage.

### I/O Input/Output (Input, Output)

The I/O pin functions as an input, output, three-state, or bi-directional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/O pins are automatically driven LOW by the Designer software.

### MODE Mode (Input)

The MODE pin controls the use of multi-function pins (DCLK, PRA, PRB, SDI). When the MODE pin is HIGH, the special functions are active. When the MODE pin is LOW, the pins function as I/Os. To provide ActionProbe capability, the

MODE pin should be terminated to GND through a 10K resistor so that the MODE pin can be pulled HIGH when required.

# NC No Connection

This pin is not connected to circuitry within the device.

## PRA Probe A (Output)

The Probe A pin is used to output data from any user-defined design node within the device. This independent diagnostic pin is used in conjunction with the Probe B pin to allow real-time diagnostic output of any signal path within the device. The Probe A pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRA is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

### PRB Probe B (Output)

The Probe B pin is used to output data from any user-defined design node within the device. This independent diagnostic pin is used in conjunction with the Probe A pin to allow real-time diagnostic output of any signal path within the device. The Probe B pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRB is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

# SDI Serial Data Input (Input)

Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

### V<sub>CC</sub> 5 V Supply Voltage HIGH supply voltage.

### RadHard Architectural Overview

The RH1280 and RH1020 architecture is composed of fine-grained building blocks which produce fast, efficient logic designs. All devices are composed of logic modules, routing resources, clock networks, and I/O modules which are the building blocks for fast logic designs.

### Logic Modules

RH1280 devices contain two types of logic modules: combinatorial (C-modules) and sequential (S-modules). RH1020 devices contain only the C-module.

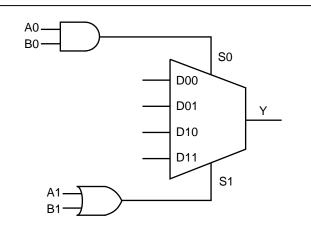

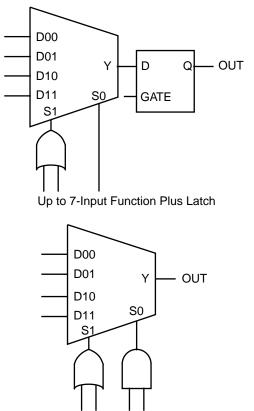

The C-module is shown in Figure 1 and implements the following function:

Y=!S1\*!S0\*D00+!S1\*S0\*D01+S1\*!S0\*D10+S1\*S0\*D11

where:

S0=A0\*B0

S1=A1+B1

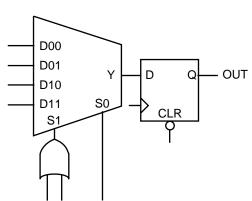

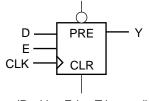

The S-module shown in Figure 2 is designed to implement high-speed sequential functions within a single logic module.

Figure 1 • C-Module Implementation

The S-module implements the same combinatorial logic function as the C-module while adding a sequential element. The sequential element can be configured as either a D flip-flop or a transparent latch. To increase flexibility, the S-module register can be by-passed so it implements purely combinatorial logic.

Up to 7-Input Function Plus D-Type Flip-Flop with Clear

Up to 4-Input Function Plus Latch with Clear

Up to 8-Input Function (Same as C-Module)

Figure 2 • S-Module Implementation

Flip-flops can also be created using two C-modules. The single event upset (SEU) characteristics differ between an S-module flip-flop and a flip-flop created using two C-modules. See the *Radiation Specifications* in this Data Sheet for details and the Actel Application Note, "Design Techniques for RadHard Field Programmable Gate Arrays."

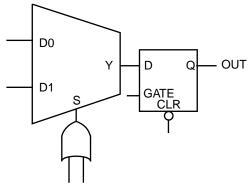

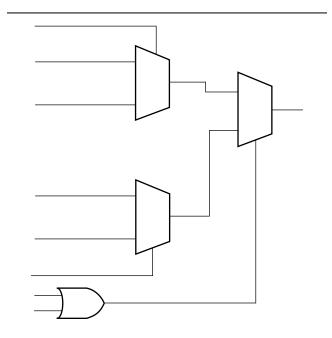

### The ACT 1 Logic Module

The ACT 1 logic module is an 8-input, one-output logic circuit chosen for the wide range of functions it implements and for its efficient use of interconnect routing resources (Figure 3).

The logic module can implement the four basic logic functions (NAND, AND, OR, and NOR) in gates of two, three, or four inputs. Each function may have many versions, with different combinations of active-low inputs. The logic module can also implement a variety of D-latches, exclusivity functions, AND-ORs, and OR-ANDs. No dedicated hardwired latches or flip-flops are required in the array, since latches and flip-flops may be constructed from logic modules wherever needed in the application.

Figure 3 • ACT 1 Logic Module

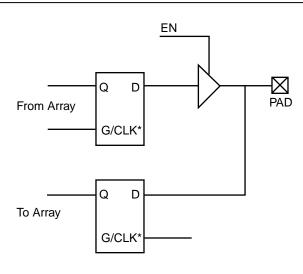

### I/O Modules

I/O modules provide the interface between the device pins and the logic array; Figure 4 is a block diagram of the I/O module. A variety of user functions, determined by a library macro selection, can be implemented in the module (refer to the Macro Library Guide for more information). I/O modules contain a tri-state buffer, and input and output latches which can be configured for input, output, or bi-directional pins (Figure 4).

\* Can be Configured as a Latch or D Flip-Flop (Using C-Module)

### Figure 4 • I/O Module

The RadHard devices contain flexible I/O structures in that each output pin has a dedicated output enable control. The I/O module can be used to latch input and/or output data, providing a fast set-up time. In addition, the Actel Designer Series software tools can build a D flip-flop, using a C-module, to register input and/or output signals.

Actel's Designer Series development tools provide a design library of I/O macros. The I/O macro library provides macro functions that can implement all I/O configurations supported by the RadHard FPGAs.

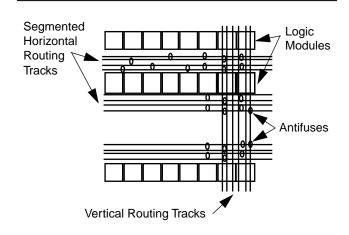

### **Routing Structure**

The RadHard device architecture uses vertical and horizontal routing tracks to interconnect the various logic and I/O modules. These routing tracks are metal interconnects that may either be of continuous length or broken into pieces called segments. Varying segment lengths allows over 90% of the circuit interconnects to be made with only two antifuse connections. Segments can be joined together at the ends, using antifuses to increase their lengths up to the full length of the track. All interconnects can be accomplished with a maximum of four antifuses.

### **Horizontal Routing**

Horizontal channels are located between the rows of modules, and are composed of several routing tracks. The horizontal routing tracks within the channel are divided into one or more segments. The minimum horizontal segment length is the width of a module-pair, and the maximum horizontal segment length is the full length of the channel. Any segment that spans more than one-third the row length is

considered a long horizontal segment. A typical channel is shown in Figure 5. Non-dedicated horizontal routing tracks are used to route signal nets. Dedicated routing tracks are used for the global clock networks, and for power and ground tie-off tracks.

### **Vertical Routing**

Another set of routing tracks run vertically through the module. Vertical tracks are of three types: input, output, and long. Vertical tracks are also divided into one or more segments. Each segment in an input track is dedicated to the input of a particular module. Each segment in an output track is dedicated to the output of a particular module. Long segments are uncommitted and can be assigned during routing. Each output segment spans four channels (two above and two below), except near the top and bottom of the array where edge effects occur. LVTs contain either one or two segments is shown in Figure 5.

### **Antifuse Structures**

An antifuse is a "normally open" structure as opposed to the normally closed fuse structure used in PROMs or PALs. The use of antifuses to implement a programmable logic device results in highly testable structures, as well as efficient programming algorithms. The structure is highly testable

### **QML Flow**

### Figure 5 • Routing Structure

because there are no pre-existing connections; therefore, temporary connections can be made using pass transistors. These temporary connections can isolate individual antifuses to be programmed, as well as isolate individual circuit structures to be tested. This can be done both before and after programming. For example, all metal tracks can be tested for continuity and shorts between adjacent tracks, and the functionality of all logic modules can be verified.

| Test Inspection                        | Method                                             |

|----------------------------------------|----------------------------------------------------|

| Wafer Lot Acceptance                   | LMFS Procedure PP525-637                           |

| Serialization                          | Required—100%                                      |

| Die Adhesion Test                      | Method 2027 (Wirebond)                             |

| Bond Pull Test                         | Method 2023 (Wirebond)                             |

| Internal Visual                        | Method 2010, Condition A                           |

| Initial Electrical Test                | Group A Subgroups 1, 7, 9                          |

| Stabake                                | Method 1008, Condition C                           |

| Temperature Cycle                      | Method 1010, Condition C, 95 Cycles Minimum        |

| Constant Acceleration                  | Method 2001, Condition D or E, Y1 Orientation Only |

| Particle Impact Noise Detection (PIND) | Method 2020, Condition A                           |

| X-Ray Radiography                      | Method 2012                                        |

| Interim Electrical Parameters          | Per Device Specification                           |

| Static Burn-In                         | Method 1015, 144 Hour Minimum, 125°C Minimum       |

| Interim Electrical Parameters          | Per Device Specification                           |

| Dynamic Burn-In                        | Method 1015, 240 Hour Minimum, 125°C Minimum       |

| Final Electrical Parameters            | Per Device Specification                           |

| Percent Defective Allowable (PDA)      | LMFS Procedure QP 2877481                          |

| Seal—Fine/Gross Leak                   | Method 1014                                        |

| External Visual (as required)          | Method 2009                                        |

| Quality Conformance Inspection (QCI)   | Quarterly Generic Data                             |

# Absolute Maximum Ratings<sup>1</sup>

### Free Air Temperature Range

| Symbol           | Parameter                               | Limits                       | Units |

|------------------|-----------------------------------------|------------------------------|-------|

| V <sub>CC</sub>  | DC Supply Voltage                       | -0.5 to +7.0                 | V     |

| VI               | Input Voltage                           | –0.5 to V <sub>CC</sub> +0.5 | V     |

| V <sub>O</sub>   | Output Voltage                          | –0.5 to V <sub>CC</sub> +0.5 | V     |

| I <sub>IO</sub>  | I/O Source/Sink<br>Current <sup>2</sup> | ±20                          | mA    |

| T <sub>STG</sub> | Storage Temperature                     | -65 to +150                  | °C    |

Notes:

- 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Device should not be operated outside the Recommended Operating Conditions.

- 2. Device inputs are normally high impedance and draw extremely low current. However, when input voltage is greater than  $V_{CC}$  + 0.5V or less than GND – 0.5V, the internal protection diode will be forward-biased and can draw excessive current.

### **Recommended Operating Conditions**

| Parameter                      |             | Units            |

|--------------------------------|-------------|------------------|

| Temperature Range <sup>1</sup> | -55 to +125 | °C               |

| Power Supply Tolerance         | ±10         | %V <sub>CC</sub> |

Notes:

1. Case temperature  $(T_C)$  is used.

### **Electrical Specifications**

|                                                | Test Conditions                                      | Crown A              | Limits |                       |       |

|------------------------------------------------|------------------------------------------------------|----------------------|--------|-----------------------|-------|

| Symbol                                         |                                                      | Group A<br>Subgroups | Min.   | Max.                  | Units |

| V <sub>OH</sub> <sup>1</sup>                   | (I <sub>OH</sub> = -4 mA)                            | 1, 2, 3              | 3.7    |                       | V     |

| V <sub>OL</sub> <sup>1</sup>                   | (I <sub>OL</sub> = 4 mA)                             | 1, 2, 3              |        | 0.4                   | V     |

| V <sub>IH</sub>                                |                                                      | 1, 2, 3              | 2.2    | V <sub>CC</sub> + 0.3 | V     |

| V <sub>IL</sub>                                |                                                      | 1, 2, 3              | -0.3   | 0.8                   | V     |

| Input Transition Time $t_R$ , $t_F^2$          |                                                      | —                    |        | 500                   | ns    |

| C <sub>IO</sub> , I/O Capacitance <sup>2</sup> |                                                      | 4                    |        | 20                    | pF    |

| I <sub>IH</sub> , I <sub>IL</sub>              | $V_{IN} = V_{CC} \text{ or GND}$<br>$V_{CC} = 5.5V$  | 1, 2, 3              | -10    | 10                    | μA    |

| I <sub>OZL</sub> , I <sub>OZH</sub>            | $V_{OUT} = V_{CC} \text{ or GND}$<br>$V_{CC} = 5.5V$ | 1, 2, 3              | -10    | 10                    | μA    |

| I <sub>CC</sub> Standby <sup>3</sup>           |                                                      | 1, 2, 3              |        | 25                    | mA    |

### Notes:

1. Only one output tested at a time.  $V_{CC} = min$ .

2. Not tested, for information only.

3. All outputs unloaded. All inputs =  $V_{CC}$  or GND.

# Radiation Specifications<sup>1, 2</sup>

| Symbol            | Characteristics                  | Conditions                                   | Min.   | Max. | Units                         |

|-------------------|----------------------------------|----------------------------------------------|--------|------|-------------------------------|

| RTD               | Total Dose                       |                                              |        | 300K | Rad(Si)                       |

| SEL               | Single Event Latch-Up            | $-55^{\circ}C \le T_{case} \le 125^{\circ}C$ |        | 0    | Fails/Device-Day              |

| SEU1 <sup>3</sup> | Single Event Upset for S-modules | $-55^{\circ}C \le T_{case} \le 125^{\circ}C$ |        | 1E-6 | Upsets/Bit-Day                |

| SEU2 <sup>3</sup> | Single Event Upset for C-modules | $-55^{\circ}C \le T_{case} \le 125^{\circ}C$ |        | 1E-7 | Upsets/Bit-Day                |

| SEU3 <sup>3</sup> | Single Event Fuse Rupture        | $-55^{\circ}C ≤ T_{case} ≤ 125^{\circ}C$     |        | <1   | FIT<br>(Fails/Device/1E9 Hrs) |

| RNF               | Neutron Fluence                  |                                              | >1E+12 |      | N/cm <sup>2</sup>             |

Notes:

1. Measured at room temperature unless otherwise stated.

2. Device electrical characteristics are guaranteed for post-irradiation levels at 25°C.

*3.* 10% worst-case particle environment, geosynchronous orbit, 0.025" of aluminum shielding. Specification set using the CREME code upset rate calculation method with a 2µm epi thickness. Reference Actel Data Book for description of S-modules and C-modules.

### **Package Thermal Characteristics**

The device junction to case thermal characteristics is  $\theta jc$ , and the junction to ambient air characteristics is  $\theta ja$ . The thermal characteristics for  $\theta ja$  are shown with two different air flow rates. Maximum junction temperature is 150°C.

A sample calculation of the maximum power dissipation for an 84-pin ceramic quad flatpack at commercial temperature is as follows:

$$\frac{Max \text{ junction temp.(°C)} - Max \text{ commercial temp.(°C)}}{\theta ja(°C/W)} = \frac{150°C - 70°C}{40°C/W} = 2.0 W$$

| Package Type          | Pin Count | θјс | θja<br>Still Air | θja<br>300 ft/min | Units |

|-----------------------|-----------|-----|------------------|-------------------|-------|

| Ceramic Quad Flatpack | 84        | 5   | 40               | 30                | °C/W  |

| Ceramic Quad Flatpack | 172       | 8   | 25               | 15                | °C/W  |

#### **General Power Equation**

$$\begin{split} P &= [I_{CC} standby + I_{CC} active] * V_{CC} + I_{OL} * V_{OL} * N + I_{OH} * \\ (V_{CC} - V_{OH}) * M \end{split}$$

Where:

$I_{CC}$  standby is the current flowing when no inputs or outputs are changing.

I<sub>CC</sub>active is the current flowing due to CMOS switching.

I<sub>OL</sub>, I<sub>OH</sub> are TTL sink/source currents.

V<sub>OL</sub>, V<sub>OH</sub> are TTL level output voltages.

N equals the number of outputs driving TTL loads to  $V_{\mbox{\scriptsize OL}}.$

M equals the number of outputs driving TTL loads to  $V_{\mbox{OH}}.$

An accurate determination of N and M is problematical because their values depend on the family type, design details, and on the system I/O. The power can be divided into two components: static and active.

### **Static Power Components**

Actel FPGAs have small static power components that result in lower power dissipation than PALs or PLDs. By integrating multiple PALs/PLDs into one FPGA, an even greater reduction in board-level power dissipation can be achieved.

The power due to standby current is typically a small component of the overall power. Standby power is calculated below for military, worst case conditions.

| I <sub>CC</sub> | V <sub>CC</sub> | Power        |

|-----------------|-----------------|--------------|

| 25 mA           | 5.5 V           | 138 mW (max) |

| 1 mA            | 5.5 V           | 5.5 mW (typ) |

### **Active Power Components**

Power dissipation in CMOS devices is usually dominated by the active (dynamic) power dissipation. This component is frequency-dependent, a function of the logic and the external I/O. Active power dissipation results from charging internal chip capacitances of the interconnect, unprogrammed antifuses, module inputs, and module outputs, plus external capacitance due to PC board traces and load device inputs. An additional component of the active power dissipation is the totem-pole current in CMOS transistor pairs. The net effect can be associated with an equivalent capacitance that can be combined with frequency and voltage to represent active power dissipation.

#### Equivalent Capacitance

The power dissipated by a CMOS circuit can be expressed by Equation 1.

Power (uW) =

$$C_{EQ} * V_{CC}^2 * F$$

(1)

Where:

$C_{EQ}$  is the equivalent capacitance expressed in pF.

V<sub>CC</sub> is the power supply in volts.

F is the switching frequency in MHz.

Equivalent capacitance is calculated by measuring ICC active at a specified frequency and voltage for each circuit component of interest. Measurements have been made over a range of frequencies at a fixed value of VCC. Equivalent capacitance is frequency-independent so the results may be used over a wide range of operating conditions. Equivalent capacitance values follow.

### **C**EQ Values for Actel FPGAs

|                                                | RH1020 | RH1280 |

|------------------------------------------------|--------|--------|

| Modules (C <sub>EQM</sub> )                    | 3.7    | 5.2    |

| Input Buffers (C <sub>EQI</sub> )              | 22.1   | 11.6   |

| Output Buffers (C <sub>EQO</sub> )             | 31.2   | 23.8   |

| Routed Array Clock Buffer Loads ( $C_{EQCR}$ ) | 4.6    | 3.5    |

To calculate the active power dissipated from the complete design, the switching frequency of each part of the logic must be known. Equation 2 shows a piece-wise linear summation over all components.

$$\begin{split} Power &= V_{CC}{}^2 * \left[ (m * C_{EQM} * f_m)_{modules} + (n * C_{EQI} * f_n)_{inputs} + (p * (C_{EQ0} + C_L) * f_p)_{outputs} + 0.5 * (q_1 * C_{EQCR} * f_{q1})_{routed\_Clk1} + (r_1 * f_{q1})_{routed\_Clk1} + 0.5 * (q_2 * C_{EQCR} * f_{q2})_{routed\_Clk2} + (r_2 * f_{q2})_{routed\_Clk2} \right] \end{split}$$

Where:

| m | = | Number | of logic | modules | switching | at f <sub>m</sub> |

|---|---|--------|----------|---------|-----------|-------------------|

|---|---|--------|----------|---------|-----------|-------------------|

- $n = Number of input buffers switching at f_n$

- $p = Number of output buffers switching at f_p$

- q1 = Number of clock loads on the first routed array clock

- q<sub>2</sub> = Number of clock loads on the second routed array clock (RH1280 only)

- r<sub>1</sub> = Fixed capacitance due to first routed array clock

- r<sub>2</sub> = Fixed capacitance due to second routed array clock (RH1280 only)

- $C_{EQM}$  = Equivalent capacitance of logic modules in pF

- C<sub>EQI</sub> = Equivalent capacitance of input buffers in pF

- $C_{EQO}$  = Equivalent capacitance of output buffers in pF

- C<sub>L</sub> = Output lead capacitance in pF

- f<sub>m</sub> = Average logic module switching rate in MHz

- f<sub>n</sub> = Average input buffer switching rate in MHz

- $f_p$  = Average output buffer switching rate in MHz

- $f_{q1}$  = Average first routed array clock rate in MHz

- $f_{q2}$  = Average second routed array clock rate in MHz (RH1280 only)

# Fixed Capacitance Values for Actel FPGAs (pF)

| Device Type | r1<br>routed_Clk1 | r2<br>routed_Clk2 |

|-------------|-------------------|-------------------|

| RH1020      | 69                | N/A               |

| RH1280      | 168               | 168               |

### **Determining Average Switching Frequency**

To determine the switching frequency for a design, you must have a detailed understanding of the data input values to the circuit. The following guidelines are meant to represent worst-case scenarios, so they can be generally used to predict the upper limits of power dissipation. These guidelines are as follows:

| Logic Modules (m)                                                  | 80% of Modules                  |

|--------------------------------------------------------------------|---------------------------------|

| Inputs Switching (n)                                               | # Inputs/4                      |

| Outputs Switching (p)                                              | # Outputs/4                     |

| First Routed Array Clock Loads $(q_1)$                             | 40% of<br>Sequential<br>Modules |

| Second Routed Array Clock Loads (q <sub>2</sub> )<br>(RH1280 only) | 40% of<br>Sequential<br>Modules |

| Load Capacitance (C <sub>L</sub> )                                 | 35 pF                           |

| Average Logic Module Switching Rate $(f_m)$                        | F/10                            |

| Average Input Switching Rate (f <sub>n</sub> )                     | F/5                             |

| Average Output Switching Rate (f <sub>p</sub> )                    | F/10                            |

| Average First Routed Array Clock Rate $(f_{q1})$                   | F                               |

| Average Second Routed Array Clock Rate $(f_{q2})$ (RH1280 only)    | F/2                             |

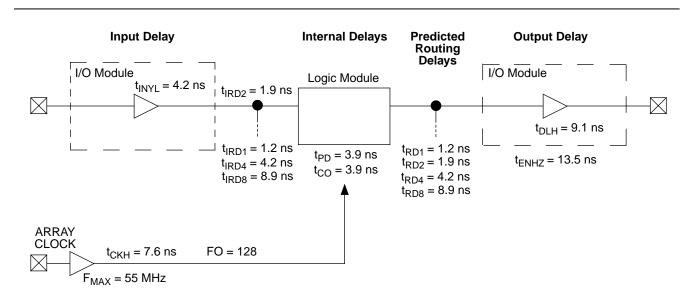

### **RH1020 Timing Module**

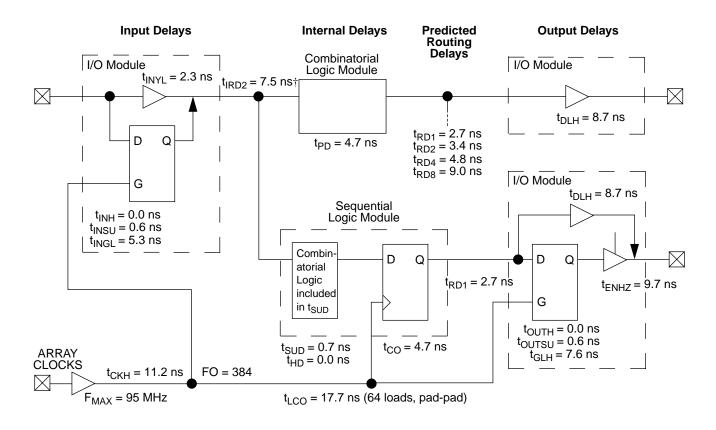

### **RH1280 Timing Model**

*† Input Module Predicted Routing Delay*

Acte

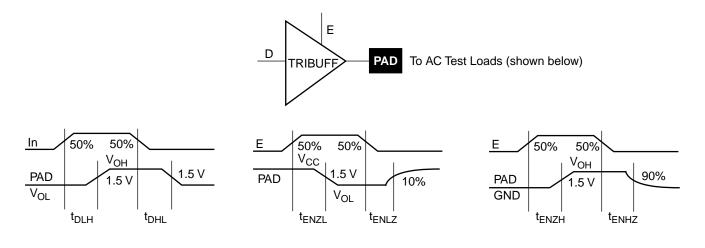

## **Parameter Measurement**

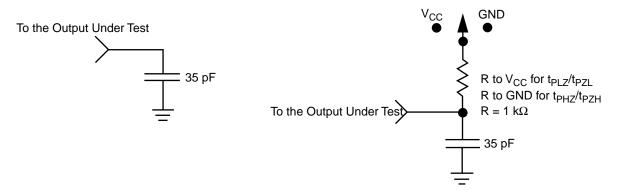

### **Output Buffer Delays**

AC Test Loads

Load 2 (Used to Measure Rising/Falling Edges)

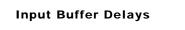

t<sub>INYL</sub>

t<sub>INYH</sub>

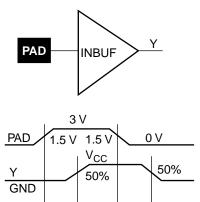

Module Delays

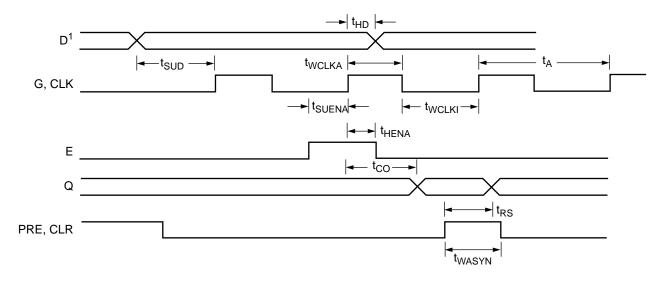

# Sequential Module Timing Characteristics

**Flip-Flops and Latches**

(Positive Edge Triggered)

*Note:* D represents all data functions involving A, B, and S for multiplexed flip-flops.

# Sequential Timing Characteristics (continued)

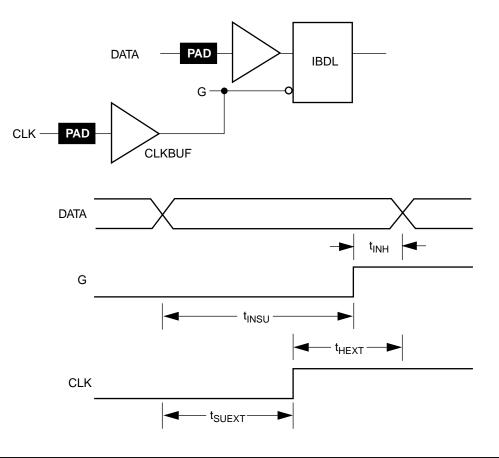

### Input Buffer Latches

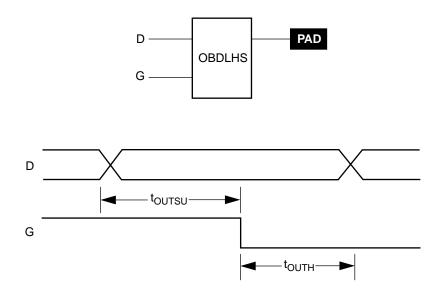

### **Output Buffer Latches**

### **RH1020 Timing Characteristics**

### (Worst-Case Military Conditions, $V_{CC}$ = 4.5 V, $T_J$ = 125°C, RTD = 300 KRAD(Si))

| Logic Module Pr              | opagation Delays                             |      |      |       |

|------------------------------|----------------------------------------------|------|------|-------|

| Parameter                    | Description                                  | Min. | Max. | Units |

| t <sub>PD1</sub>             | Single Module                                |      | 3.9  | ns    |

| t <sub>PD2</sub>             | Dual Module Macros                           |      | 9.2  | ns    |

| t <sub>co</sub>              | Sequential Clock to Q                        |      | 3.9  | ns    |

| t <sub>GO</sub>              | Latch G to Q                                 |      | 3.9  | ns    |

| t <sub>RS</sub>              | Flip-Flop (Latch) Reset to Q                 |      | 3.9  | ns    |

| Predicted Routin             | ng Delays <sup>1</sup>                       |      |      |       |

| t <sub>RD1</sub>             | FO=1 Routing Delay                           |      | 1.2  | ns    |

| t <sub>RD2</sub>             | FO=2 Routing Delay                           |      | 1.9  | ns    |

| t <sub>RD3</sub>             | FO=3 Routing Delay                           |      | 2.8  | ns    |

| t <sub>RD4</sub>             | FO=4 Routing Delay                           |      | 4.2  | ns    |

| t <sub>RD8</sub>             | FO=8 Routing Delay                           |      | 8.9  | ns    |

| Sequential Timin             | g Characteristics <sup>2</sup>               |      |      |       |

| t <sub>SUD</sub>             | Flip-Flop (Latch) Data Input Set-Up          | 7.5  |      | ns    |

| t <sub>HD</sub> <sup>3</sup> | Flip-Flop (Latch) Data Input Hold            | 0.0  |      | ns    |

| t <sub>SUENA</sub>           | Flip-Flop (Latch) Enable Set-Up              | 7.5  |      | ns    |

| t <sub>HENA</sub>            | Flip-Flop (Latch) Enable Hold                | 0.0  |      | ns    |

| t <sub>WCLKA</sub>           | Flip-Flop (Latch) Clock Active Pulse Width   | 9.2  |      | ns    |

| t <sub>WASYN</sub>           | Flip-Flop (Latch) Asynchronous Pulse Width   | 9.2  |      | ns    |

| t <sub>A</sub>               | Flip-Flop Clock Input Period                 | 19.2 |      | ns    |

| f <sub>MAX</sub>             | Flip-Flop (Latch) Clock Frequency (FO = 128) |      | 50   | MHz   |

Notes:

1. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

2. Set-up times assume fanout of 3. Further testing information can be obtained from the DirectTime Analyzer utility.

3. The hold time for the DFME1A macro may be greater than 0 ns. Use the Designer Series 3.0 (or later) Timer to check the hold time for this macro.

### **RH1020 Timing Characteristics (continued)**

### (Worst-Case Military Conditions)

| Input Module P    | Propagation Delays                   |                     |              |            |     |

|-------------------|--------------------------------------|---------------------|--------------|------------|-----|

| Parameter         | Description                          | Min.                | Max.         | Units      |     |

| t <sub>INYH</sub> | Pad to Y High                        |                     |              | 4.2        | ns  |

| t <sub>INYL</sub> | Pad to Y Low                         |                     | 4.2          | ns         |     |

| Input Module P    | redicted Routing Delays <sup>1</sup> |                     |              |            |     |

| t <sub>IRD1</sub> | FO=1 Routing Delay                   |                     |              | 1.2        | ns  |

| t <sub>IRD2</sub> | FO=2 Routing Delay                   |                     |              | 1.9        | ns  |

| t <sub>IRD3</sub> | FO=3 Routing Delay                   |                     |              | 2.8        | ns  |

| t <sub>IRD4</sub> | FO=4 Routing Delay                   |                     |              | 4.2        | ns  |

| t <sub>IRD8</sub> | FO=8 Routing Delay                   |                     |              | 8.9        | ns  |

| Global Clock N    | etwork                               |                     |              |            |     |

| t <sub>CKH</sub>  | Input Low to High                    | FO = 16<br>FO = 128 |              | 6.6<br>7.6 | ns  |

| t <sub>CKL</sub>  | Input High to Low                    | FO = 16<br>FO = 128 |              | 8.7<br>9.5 | ns  |

| t <sub>PWH</sub>  | Minimum Pulse Width High             | FO = 16<br>FO = 128 | 8.8<br>9.2   |            | ns  |

| t <sub>PWL</sub>  | Minimum Pulse Width<br>Low           | FO = 16<br>FO = 128 | 1.6<br>2.4   |            | ns  |

| t <sub>CKSW</sub> | Maximum Skew                         | FO = 16<br>FO = 128 |              | 1.6<br>2.5 | ns  |

| t <sub>P</sub>    | Minimum Period                       | FO = 16<br>FO = 128 | 17.9<br>19.2 |            | ns  |

| f <sub>MAX</sub>  | Maximum Frequency                    | FO = 16<br>FO = 128 |              | 55<br>50   | MHz |

Note:

1. These parameters should be used for estimating device performance. Optimization techniques may further reduce delays by 0 to 4 ns. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

# RH1020 Timing Characteristics (continued)

### (Worst-Case Military Conditions)

| Output Module     | Timing                     |      |      |       |

|-------------------|----------------------------|------|------|-------|

| Parameter         | Description                | Min. | Max. | Units |

| TTL Output Mo     | dule Timing <sup>1</sup>   |      |      |       |

| t <sub>DLH</sub>  | Data to Pad High           |      | 9.1  | ns    |

| t <sub>DHL</sub>  | Data to Pad Low            |      | 10.2 | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to High       |      | 8.9  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to Low        |      | 10.7 | ns    |

| t <sub>ENHZ</sub> | Enable Pad High to Z       |      | 13.5 | ns    |

| t <sub>ENLZ</sub> | Enable Pad Low to Z        |      | 12.2 | ns    |

| d <sub>TLH</sub>  | Delta Low to High          |      | 0.08 | ns/pF |

| d <sub>THL</sub>  | Delta High to Low          |      | 0.11 | ns/pF |

| CMOS Output N     | Module Timing <sup>1</sup> |      |      |       |

| t <sub>DLH</sub>  | Data to Pad High           |      | 10.7 | ns    |

| t <sub>DHL</sub>  | Data to Pad Low            |      | 8.7  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to High       |      | 8.1  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to Low        |      | 11.2 | ns    |

| t <sub>ENHZ</sub> | Enable Pad High to Z       |      | 13.5 | ns    |

| t <sub>ENLZ</sub> | Enable Pad Low to Z        |      | 12.2 | ns    |

| d <sub>TLH</sub>  | Delta Low to High          |      | 0.14 | ns/pF |

| d <sub>THL</sub>  | Delta High to Low          |      | 0.08 | ns/pF |

Notes:

1. Delays based on 35 pF loading.

2. SSO information can be found in the "Simultaneous Switching Output Limits for Actel FPGAs" Application Note in the 1996 Actel Data Book.

# **RH1280 Timing Characteristics**

### (Worst-Case Military Conditions, V<sub>CC</sub> = 4.5 V, T<sub>J</sub> = 125°C, RTD = 300 KRAD(Si))

| Logic Module P     | ropagation Delays <sup>1</sup>             |                                |      |       |  |

|--------------------|--------------------------------------------|--------------------------------|------|-------|--|

| Parameter          | Description                                | Min.                           | Max. | Units |  |

| t <sub>PD1</sub>   | Single Module                              |                                | 4.7  | ns    |  |

| t <sub>co</sub>    | Sequential Clk to Q                        |                                | 4.7  | ns    |  |

| t <sub>GO</sub>    | Latch G to Q                               |                                | 4.7  | ns    |  |

| t <sub>RS</sub>    | Flip-Flop (Latch) Reset to Q               | ip-Flop (Latch) Reset to Q 4.7 |      | ns    |  |

| Predicted Routin   | ng Delays <sup>2</sup>                     |                                |      |       |  |

| t <sub>RD1</sub>   | FO=1 Routing Delay                         |                                | 2.7  | ns    |  |

| t <sub>RD2</sub>   | FO=2 Routing Delay                         |                                | 3.4  | ns    |  |

| t <sub>RD3</sub>   | FO=3 Routing Delay                         |                                | 4.1  | ns    |  |

| t <sub>RD4</sub>   | FO=4 Routing Delay                         |                                | 4.8  | ns    |  |

| t <sub>RD8</sub>   | FO=8 Routing Delay                         |                                | 9.0  | ns    |  |

| Sequential Timir   | ng Characteristics <sup>3,4</sup>          |                                |      |       |  |

| t <sub>SUD</sub>   | Flip-Flop (Latch) Data Input Set-Up        | 0.7                            |      | ns    |  |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data Input Hold          | 0.0                            |      | ns    |  |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Set-Up            | 1.4                            |      | ns    |  |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold              | 0.0                            |      | ns    |  |

| t <sub>WCLKA</sub> | Flip-Flop (Latch) Clock Active Pulse Width | 6.6                            |      | ns    |  |

| t <sub>WASYN</sub> | Flip-Flop (Latch) Asynchronous Pulse Width | 6.6                            |      | ns    |  |

| t <sub>A</sub>     | Flip-Flop Clock Input Period               | 13.5                           |      | ns    |  |

| t <sub>INH</sub>   | Input Buffer Latch Hold                    | 0.0                            |      | ns    |  |

| t <sub>INSU</sub>  | Input Buffer Latch Set-Up                  | 0.6                            |      | ns    |  |

| t <sub>оитн</sub>  | Output Buffer Latch Hold                   | 0.0                            |      | ns    |  |

| t <sub>outsu</sub> | Output Buffer Latch Set-Up                 | 0.6                            |      | ns    |  |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Clock Frequency          |                                | 95   | MHz   |  |

Notes:

1. For dual-module macros, use  $t_{PD1} + t_{RD1} + t_{PDn}$ ,  $t_{CO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the DirectTime Analyzer utility.

4. Set-up and hold timing parameters for the input buffer latch are defined with respect to the PAD and the D input. External set-up/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G input subtracts (adds) to the internal set-up (hold) time.

### **RH1280 Timing Characteristics (continued)**

### (Worst-Case Military Conditions)

| Input Module Pr    | opagation Delays                     |                     |              |             |     |

|--------------------|--------------------------------------|---------------------|--------------|-------------|-----|

| Parameter          | Description                          | Min.                | Max.         | Units       |     |

| t <sub>INYH</sub>  | Pad to Y High                        |                     |              | 1.9         | ns  |

| t <sub>INYL</sub>  | Pad to Y Low                         |                     |              | 2.3         | ns  |

| t <sub>INGH</sub>  | G to Y High                          |                     |              | 4.1         | ns  |

| t <sub>INGL</sub>  | G to Y Low                           |                     |              | 5.3         | ns  |

| Input Module Pr    | redicted Routing Delays <sup>1</sup> |                     |              |             |     |

| t <sub>IRD1</sub>  | FO=1 Routing Delay                   |                     |              | 6.8         | ns  |

| t <sub>IRD2</sub>  | FO=2 Routing Delay                   |                     |              | 7.5         | ns  |

| t <sub>IRD3</sub>  | FO=3 Routing Delay                   |                     |              | 8.2         | ns  |

| t <sub>IRD4</sub>  | FO=4 Routing Delay                   |                     |              | 8.9         | ns  |

| t <sub>IRD8</sub>  | FO=8 Routing Delay                   |                     |              | 11.7        | ns  |

| Global Clock Ne    | etwork                               |                     |              |             |     |

| t <sub>CKH</sub>   | Input Low to High                    | FO = 32<br>FO = 384 |              | 9.6<br>11.2 | ns  |

| <sup>t</sup> CKL   | Input High to Low                    | FO = 32<br>FO = 384 |              | 9.6<br>11.2 | ns  |

| t <sub>PWH</sub>   | Minimum Pulse Width High             | FO = 32<br>FO = 384 | 5.8<br>6.2   |             | ns  |

| t <sub>PWL</sub>   | Minimum Pulse Width Low              | FO = 32<br>FO = 384 | 5.8<br>6.2   |             | ns  |

| t <sub>CKSW</sub>  | Maximum Skew                         | FO = 32<br>FO = 384 |              | 1.1<br>1.1  | ns  |

| t <sub>SUEXT</sub> | Input Latch External Set-Up          | FO = 32<br>FO = 384 | 0.0<br>0.0   |             | ns  |

| t <sub>HEXT</sub>  | Input Latch External Hold            | FO = 32<br>FO = 384 | 4.6<br>5.8   |             | ns  |

| t <sub>P</sub>     | Minimum Period                       | FO = 32<br>FO = 384 | 11.8<br>13.0 |             | ns  |

| f <sub>MAX</sub>   | Maximum Frequency                    | FO = 32<br>FO = 384 |              | 105<br>95   | MHz |

Note:

1. These parameters should be used for estimating device performance. Optimization techniques may further reduce delays by 0 to 4 ns. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

# RH1280 Timing Characteristics (continued)

### (Worst-Case Military Conditions)

| Output Module                         | Γiming                                             |      |      |       |

|---------------------------------------|----------------------------------------------------|------|------|-------|

| Parameter                             | Description                                        | Min. | Max. | Units |

| TTL Output Module Timing <sup>1</sup> |                                                    |      |      |       |

| t <sub>DLH</sub>                      | Data to Pad High                                   |      | 6.8  | ns    |

| t <sub>DHL</sub>                      | Data to Pad Low                                    |      | 7.6  | ns    |

| t <sub>ENZH</sub>                     | Enable Pad Z to High                               |      | 6.8  | ns    |

| t <sub>ENZL</sub>                     | Enable Pad Z to Low                                |      | 7.6  | ns    |

| t <sub>ENHZ</sub>                     | Enable Pad High to Z                               |      | 9.7  | ns    |

| t <sub>ENLZ</sub>                     | Enable Pad Low to Z                                |      | 9.7  | ns    |

| t <sub>GLH</sub>                      | G to Pad High                                      |      | 7.6  | ns    |

| t <sub>GHL</sub>                      | G to Pad Low                                       |      | 8.9  | ns    |

| t <sub>LCO</sub>                      | I/O Latch Clock-Out (Pad-to-Pad), 64 Clock Loading |      | 17.7 | ns    |

| t <sub>ACO</sub>                      | Array Clock-Out (Pad-to-Pad), 64 Clock Loading     |      | 25.0 | ns    |

| d <sub>TLH</sub>                      | Capacitive Loading, Low to High                    |      | 0.07 | ns/pF |

| d <sub>THL</sub>                      | Capacitive Loading, High to Low 0.09               |      |      |       |

| CMOS Output M                         | lodule Timing <sup>1</sup>                         |      |      |       |

| t <sub>DLH</sub>                      | Data to Pad High                                   |      | 8.7  | ns    |

| t <sub>DHL</sub>                      | Data to Pad Low                                    |      | 6.4  | ns    |

| t <sub>ENZH</sub>                     | Enable Pad Z to High                               |      | 6.8  | ns    |

| t <sub>ENZL</sub>                     | Enable Pad Z to Low                                |      | 7.6  | ns    |

| t <sub>ENHZ</sub>                     | Enable Pad High to Z                               |      | 9.7  | ns    |

| t <sub>ENLZ</sub>                     | Enable Pad Low to Z                                |      | 9.7  | ns    |

| t <sub>GLH</sub>                      | G to Pad High                                      |      | 7.6  | ns    |

| t <sub>GHL</sub>                      | G to Pad Low                                       |      | 8.9  | ns    |

| t <sub>LCO</sub>                      | I/O Latch Clock-Out (Pad-to-Pad), 64 Clock Loading |      | 20.1 | ns    |

| t <sub>ACO</sub>                      | Array Clock-Out (Pad-to-Pad), 64 Clock Loading     |      | 29.5 | ns    |

| d <sub>TLH</sub>                      | Capacitive Loading, Low to High                    |      | 0.09 | ns/pF |

| d <sub>THL</sub>                      | Capacitive Loading, High to Low                    |      | 0.08 | ns/pF |

Notes:

1. Delays based on 35 pF loading.

2. SSO information can be found in the "Simultaneously Switching Output Limits for Actel FPGAs" Application Note in the 1996 Actel Data Book.

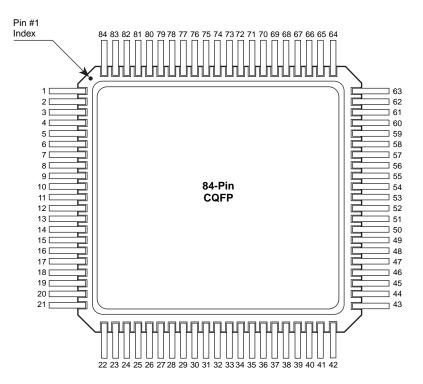

### **Package Pin Assignments**

### 84-Pin CQFP (Top View)

| Function            | RH1020 Pin Number          |

|---------------------|----------------------------|

| CLKA or I/O         | 53                         |

| DCLK or I/O         | 62                         |

| GND                 | 7, 8, 29, 49, 50, 71       |

| MODE                | 55                         |

| N/C (No Connection) | 1                          |

| PRA or I/O          | 63                         |

| PRB or I/O          | 64                         |

| SDI or I/O          | 61                         |

| V <sub>CC</sub>     | 14, 15, 22, 35, 56, 57, 77 |

- 1. MODE should be terminated to GND through a 10K resistor to enable ActionProbe usage; otherwise, it can be terminated directly to GND.

- 2. Unused I/O pins are designated as outputs by Designer and are driven LOW.

- 3. All unassigned pins are available for use as I/Os

- 4. The V<sub>PP</sub>, V<sub>KS</sub>, and V<sub>SV</sub> pin names have been modified to reflect the normal system state (V<sub>CC</sub> or GND) for these programming pins.

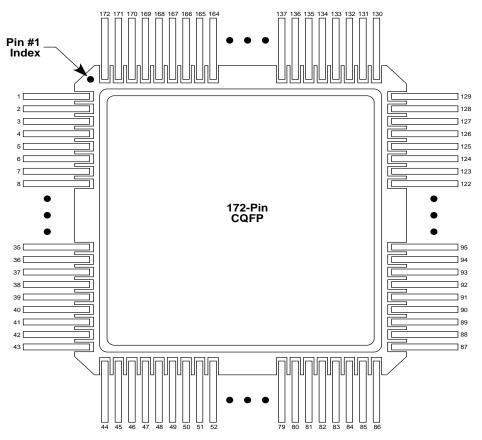

### Package Pin Assignments (continued)

### 172-Pin CQFP (Top View)

| Function        | RH1280 Pin Number                                                         |

|-----------------|---------------------------------------------------------------------------|

| CLKA or I/O     | 150                                                                       |

| CLKB or I/O     | 154                                                                       |

| DCLK or I/O     | 171                                                                       |

| GND             | 7, 17, 22, 32, 37, 55, 65, 75, 98, 103, 106, 108, 118, 123, 141, 152, 161 |

| MODE            | 1                                                                         |

| PRA or I/O      | 148                                                                       |

| PRB or I/O      | 156                                                                       |

| SDI or I/O      | 131                                                                       |

| V <sub>CC</sub> | 12, 23, 24, 27, 50, 66, 80, 107, 109, 110, 113, 136, 151, 166             |

- 1. Unused I/O pins are designated as outputs by Designer and are driven LOW.

- 2. All unassigned pins are available for use as I/Os.

- 3. MODE should be terminated to GND through a 10K resistor to enable ActionProbe usage; otherwise, it can be terminated directly to GND.

- 4. The V<sub>PP</sub>, V<sub>KS</sub>, and V<sub>SV</sub> pin names have been modified to reflect the normal system state (V<sub>CC</sub> or GND) for these programming pins.

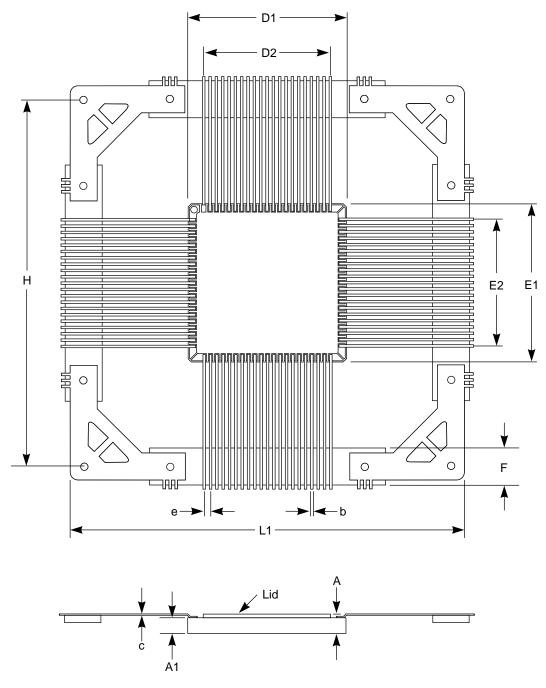

# Package Mechanical Drawings

### Ceramic Quad Flatpack (84-Pin CQFP)

- 1. Dimensions are in inches.

- 2. Seal Ring and Lid are connected to Ground.

- 3. Lead material is Kovar with gold plate over nickel.

- 4. Packages are shipped unformed with the ceramic tie bar in a test carrier.

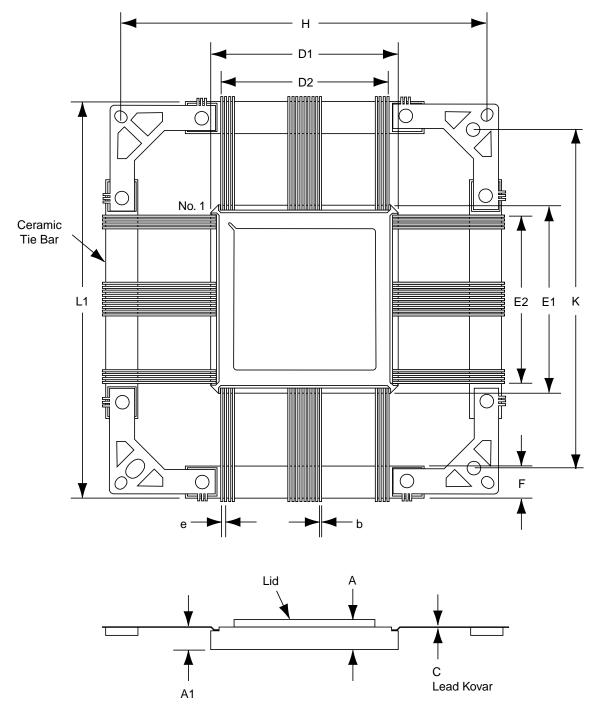

### Package Mechanical Drawings (continued)

Ceramic Quad Flatpack (CQFP—Cavity Up)

- 1. All dimensions are in inches except CQ208 and CQ256 which are in millimeters.

- 2. Outside leadframe holes (from dimension H) are circular for the CQ208 and CQ256.

- 3. Seal ring and lid are connected to Ground.

- 4. Lead material is Kovar with minimum 60 miconiches gold over nickel.

- 5. Packages are shipped unformed with the ceramic tie bar.

- 6. 32200DX CQ208 has heat sink on the backside.

|        | CQ84      |       |           | CQ172     |           |       |

|--------|-----------|-------|-----------|-----------|-----------|-------|

| Symbol | Min       | Nom.  | Мах       | Min       | Nom.      | Мах   |

| A      | 0.070     | 0.090 | 0.100     | 0.094     | 0.105     | 0.116 |

| A1     | 0.060     | 0.075 | 0.080     | 0.080     | 0.090     | 0.100 |

| b      | 0.008     | 0.010 | 0.012     | 0.007     | 0.008     | 0.010 |

| с      | 0.004     | 0.006 | 0.008     | 0.004     | 0.006     | 0.008 |

| D1/E1  | 0.640     | 0.650 | 0.660     | 1.168     | 1.180     | 1.192 |

| D2/E2  | 0.500 BSC |       |           |           | 1.050 BSC | ;     |

| е      | 0.025 BSC |       |           | (         | 0.025 BSC | ;     |

| F      | 0.130     | 0.140 | 0.150     | 0.175     | 0.200     | 0.225 |

| Н      | 1.460 BSC |       | 2.320 BSC |           |           |       |

| К      |           | _     |           | 2.140 BSC |           |       |

| L1     | 1.595     | 1.600 | 1.615     | 2.485     | 2.495     | 2.505 |

### Ceramic Quad Flatpack (CQFP)

Note:

1. All dimensions are in inches except CQ208 and CQ256, which is in millimeters.

2. BSC equals Basic Spacing between Centers. This is a theoretical true position dimension and so has no tolerance.

# Actel and the Actel logo are registered trademarks of Actel Corporation. All other trademarks are the property of their owners.

http://www.actel.com

## Actel Europe Ltd.

Daneshill House, Lutyens Close Basingstoke, Hampshire RG24 8AG United Kingdom **Tel:** +44.(0)1256.305600 **Fax:** +44.(0)1256.355420

### **Actel Corporation**

955 East Árques Avenue Sunnyvale, California 94086 USA **Tel:** 408.739.1010 **Fax:** 408.739.1540

### Actel Asia-Pacific

EXOS Ebisu Bldg. 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150 Japan **Tel:** +81.(0)3.3445.7671 **Fax:** +81.(0)3.3445.7668