![]()

작성일: 2005.11.9

![]()

알버트 타이(Albert Tai)|액텔 APAC 지역 테크니컬 매니저, FAE

시스템 설계 비용 절감 및 설계 주기 단축에 대한 계속되는 압박은 시스템의 고효율, 모듈화, 단순화의 동인으로 작용한다. 어떠한 특성이 애플리케이션에 요구될 때, 일반적으로 설계자는 시스템 요구 사항을 충족할 만한 솔루션과 관련이 있는 시장을 탐색하기 마련이다.

설계 요구사항을 만족하는 솔루션에 대한 선택의 범위가 좁혀지면, 설계자는 비용과 설계 단순성에 근거하여 가장 적합한 대안을 선택한다.

일단, 시스템에 전원이 인가되면 시스템 부품은 초기화되고 시스템 관리 작업이 수행된다. 일부 애플리케이션에서는 시스템이 바로 작동할 수 있도록 빠른 초기화 시간이 요구되기도 한다. 인명 구조 장비처럼 중요한 기능을 수행하는 의료 및 산업 애플리케이션이 여기에 해당한다. 파워업·파워다운의 주기가 잦은 배터리 구동 방식의 휴대형 애플리케이션의 경우, 사용자가 제품을 바로 사용할 수 있도록 초기화 시간을 단축할 필요가 있다.

LAPU 디바이스

시스템은 상호 의존성이 높은 여러 개의 부품으로 구성되기 때문에 이들 부품들이 잘 작동하도록 하는 것이 설계자의 임무이다. 효율적인 시스템 구동을 위해서는 시스템의 핵심 경로에 LAPU(Live at Power-up) 디바이스를 선택하는 것이 무엇보다 중요하다. LAPU 디바이스는 시스템 전압이 최소치에 도달하기 전, 즉 파워업 단계라고 정의되는 시점에 구동하기 때문에 전원이 인가된 후에 작동하는 디바이스와는 정반대의 의미를 갖는다. 예컨대 클럭 분산 업무용 통합 PLL(Phased Locked Loop)이 내장된 LAPU 디바이스를 선택한다면, 시스템의 전체 스타트업 시간을 단축할 수 있을 뿐만 아니라 이러한 기능을 수행하기 위해 독립형 PLL을 사용할 필요가 없다.

PLD 대안

PLD(Programmable Logic Device)는 출시 기간의 단축, ISP(In System Programming) 능력, 사용 용이성, 신속한 프로토타이핑 등의 장점으로 인해 급속히 성장하고 있다. 기술의 발전으로 PLD 가격이 엄청나게 낮아짐에 따라 LAPU ASIC은 시스템 설계에서 PLD에 점점 자리를 빼앗기는 신세가 되고 말았다.

시스템에 PLD가 필요할 경우, 설계자는 선택한 PLD의 LAPU 속성을 무시해서는 안 된다. 이러한 판단은 자칫 시스템 크기와 비용을 불필요하게 증가시킬 수 있다. PLD의 경우, 디바이스 초기화 및 구동에 필요한 컨피규레이션 메모리를 요구한다. 현재 시중에는 칩에 컨피규레이션 파일을 저장할 수 있는 비휘발성 메모리, 예컨대 플래시, EEPROM, 안티퓨즈(Anti-Fuse) 기반의 다양한 PLD 솔루션이 공급되고 있다. 이러한 솔루션은 컨피규레이션 파일을 별도로 다운로드 할 필요가 없기 때문에 ASSP(Application Specific standard Product)와 ASIC처럼 디바이스를 곧바로 작동시켜 사용할 수 있다.

휘발성인 SRAM 기반의 PLD 같은 다른 기술은 미지의 상태에서 활성화되기 때문에 전원을 켤 때마다 외부 비휘발성 메모리로부터 컨피규레이션을 해줄 필요가 있다. 이 밖에 SRAM FPGA 아키텍처와 비휘발성 컨피규레이션 메모리 온 칩이 내장된 하이브리드 SRAM 디바이스도 있다. 하이브리드 FPGA는 전원을 켤 때마다 반드시 내부에서 로딩해야 한다.

이 디바이스는 컨피규레이션이 끝나고 나서야 고객 애플리케이션에 따라 구동을 시작한다. 하이브리드 디바이스의 경우 전원이 꺼지거나 전원이 저하될 때마다 컨피규레이션이 지워지기 때문에 나중에 전원을 켤 때에 컨피규레이션 파일을 다시 로딩해야 한다.

LAPU PLD를 사용하면 설계에 들이는 노력을 줄일 수 있다. 이 PLD는 시스템 환경 초기화 및 셋업을 지원하고, 마이크로컨트롤러 및 기타 시스템 동작을 위한 준비를 하기 때문에 시스템 초기화 시간을 줄일 수 있다. 시스템 메모리 구성, 시스템 보드의 부품에 대한 일관되고 신뢰할 수 있는 파워업 시퀀스 제공, 디바이스에 대한 클럭 분배, 인터페이스 및 버스 활동 관리와 같은 셋업 작업들을 통해 더욱 효율적인 설계는 물론 부품 수 및 전력 소모 감소를 실현할 수 있다.

디바이스 분류

설계자는 디바이스 분류 시스템을 적용하여 시스템 내 반도체 디바이스의 파워업 반응을 파악할 수 있다. 이 분류 시스템은 설계자가 시스템에 전원을 연결하는 단계에서 구동과 기능성을 고려하여 해당 애플리케이션에 적합한 프로그래머블 로직 부품을 선택할 수 있도록 돕는다.

전압 트리거 포인트가 낮은 시스템 부품은 동작을 시작하고 시스템 내에서 초기화, 전력 관리, 핵심 시스템 업무를 지원하며, 클럭 및 리셋 신호를 제공한다. 파워온과 파워업 사이에 구동하는 디바이스는 레벨 0 LAPU를 지원하는 것으로 판단한다. 레벨 0 LAPU을 만족하는 디바이스는 NVM(Non-volatile Memory) PLD와 ASIC이며, 일부 ASSP도 여기에 해당된다. 컨피규레이션 파일을 다운로드 해야 하거나 구동 시 높은 레벨의 시스템 전압이 최소한도로 요구되는 디바이스는 파워업 이후에 작동하기 때문에 레벨 1 LAPU로 분류된다.

레벨 1 LAPU는 보통 ASSP이거나, 아니면 메모리나 인터페이스를 메인 프로세서에 설정하는 데 사용되는 디바이스다. 시스템 환경을 초기화하여 클럭, 리셋, 인터페이스 및 메모리가 준비되면 프로세서(MCU/CPU)는 동작을 시작하여 필요한 주변장치에 접속한다. 이들 디바이스는 시스템 초기화 후에 작동하기 때문에 레벨 2를 지원한다.

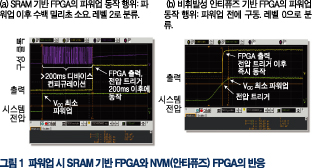

그림 1의 NVM(안티 퓨즈) FPGA AX250 I/O는 시스템에 전원이 인가되기 전에 작동한다. SRAM FPGA XC3S200의 경우, 부품이 컨피규레이션 파일을 다운로드 하여 I/O 동작을 시작하는데 200ms 이상이 걸린다. NVM FPGA는 레벨 0 LAPU로 분류되며, 레벨 2 LAPU로 분류되는 SRAM FPGA보다 일반적으로 4,000배 정도 빠르다.

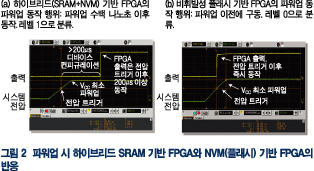

그림 2의 NVM(플래시) FPGA A3PE600 I/O는 시스템 파워업 이전에 작동하며, 하이브리드 SRAM FPGA EPM1270의 경우, 컨피규레이션 파일 로딩과 작동 시작까지 200µs 정도가 걸린다.

하이브리드(SRAM + NVM) FPGA는 전원을 연결한 후에 컨피규레이션을 해 주어야 하며, 파워업 이후에는 레벨 1 라이브에 맞추어야 한다. 플래시 FPGA는 램프업 속도에 관계없이 레벨 0 LAPU에 맞추어야 하며, 일반적으로 20~40배 정도 빠르다.

램프업 시간이 상이한 NVM FPGA와 SRAM FPGA의 구동시간을 비교해 보면, 램프업 속도 측면에서 NVM FPGA가 우수하다는 것을 알 수 있다. 램프업 시간 비율이 다른 NVM FPGA와 SRAM 하이브리드 FPGA간의 파워업 구동시간과 램프업 시간을 비교하면 고속 동작 시 NVM FPGA의 램프업 속도가 더 빠르다는 것을 알 수 있다.

테스트를 거친 비휘발성 FPGA는 항상 파워업 이후에 작동하며, 디바이스의 로직 크기가 파워온에서 구동까지 걸리는 시간에 영향을 끼치지는 않는다. 이에 반해 SRAM과 하이브리드 디바이스는 파워온에서 구동까지 걸리는 시간이 길다. 디바이스의 컨피규레이션 파일 크기가 디바이스의 로직 밀도에 따라 달라지기 때문이다. 따라서 디바이스 밀도가 큰 경우, NVM과 SRAM간 차이는 상당히 커진다.

시스템 기능 차이

시스템 아키텍처는 PLD가 지원하는 LAPU 레벨에 따라 달라진다. SRAM FPGA를 외부 플래시에서 로딩하여 실행하는 경우, SRAM 디바이스가 컨피규레이션을 로딩하여 구동을 시작하기까지 시간이 걸리기 때문에 시스템은 수백 밀리초가 지난 후에 작동한다.

NVM FPGA를 사용해 시스템을 구현한다는 말은 파워업 이후에 비휘발성 FPGA에 대한 컨피규레이션을 할 필요가 없기 때문에 시스템이 수백 밀리초가 아니라 50µs가 지난 후에 구동한다는 것을 의미한다.

LAPU 기능은 시스템 단순화의 이점을 제공하는 것 외에도 보드에 탑재하는 부품의 수를 줄일 수 있기 때문에 소비전력 감소, 총시스템 비용 절감, 신뢰성 향상 등을 기할 수 있다.

SRAM 기반 FPGA의 경우 중요 회로가 추가적으로 필요할 수 있다. 시스템 설정과 관리업무에 부팅용 PROM 또는(및) 비안전 설정 코드용 시스템 부가 메모리, 즉 LAPU CPLD가 필요한 경우도 있다. 또한 보드에 탑재된 부품의 초기화를 위해 파워업을 한 후 클럭 및 리셋 신호를 발생시킬 필요가 있다. 시스템 설계가 복잡해지고 비용이 증가하며, 개발 프로세스가 지연되는 이유도 여기에 있다.

비휘발성 FPGA를 사용하면 보드 및 시스템 설계를 단순화하고 비용을 절감할 수 있다. 레벨 2 LAPU SRAM FPGA를 사용할 경우 시스템 평균비용은 레벨 0 LAPU 비휘발성 FPGA를 이용한 시스템에 비해 3배나 높다.

![]()