Second Prize

# Portable Telemedicine Monitoring Equipment

Institution: HuaQiao University Participants: Huafeng Hong, Qianjiang, Yongjie Li Instructor: Ling Chaodong

## **Design Introduction**

For our design, we wanted to provide a specialized in-home medical monitoring system. The following sections provide background information about health issues and telemedicine.

## Background

Our project focuses on several issues, including:

- Medical—In medicine today, the focus has shifted from disease treatment to prevention and health care. People care more about their health, and while disease prevention and health care have become an indispensable part of their lives, daily care for current physical conditions can eliminate problems and pain that could result from untreated conditions.

- Social—With increasing attention on health and technological progress both home and abroad, home health care engineering (HHCE) is an emerging discipline. It advocates the concepts of medical treatment at home, self health care, and remote diagnosis, and combines technology with medical treatment. While addressing the trends of an aging society, soaring medical expenses, and increasing health demands in the 21st century, HHCE enables medical resource sharing and improves medical care in remote areas, making it well received by society.

- *Technological*—Modern science and technology provides a technological basis for these designs. Embedded technology provides a leap forward and enables a diverse array of electronic products. Meanwhile, advancing network communications allows networked devices to share all kinds of

information easily. With improving manufacturing processes, chips are becoming more integrated and the resulting products are more portable and simplified.

## Telemedicine

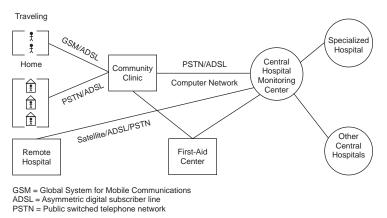

Telemedicine, which integrates network and medical technology, generally comprises remote diagnosis, expert consultation, information service, online checkups, remote communication, etc. Based on computers and network communication, it implements remote transfer, storage, query, comparison, display, and sharing of medical data, video, and audio information. See Figure 1.

Figure 1. Telemedicine Networking Structure

Telemedicine has the following benefits:

- When used for home health care at the proper location, telemedicine can greatly reduce the time and cost of transporting patients.

- Medical centers, receiving photos, can perform management and home medical service assignments.

- Doctors can share medical records and diagnosis photos without geographical barriers, contributing to clinical research development.

- Medical staff in remote areas can receive better medical education.

## **Design Considerations**

Our design accounts for the following considerations:

- The existing medical, social, and technological background shows that medical monitoring is moving towards personalized, portable, multi-functional systems. Systems and equipment are needed to meet this trend, which is the starting point of this design.

- Telemedicine will expand the network of existing HHCE equipment to every corner of the world. Benefits of telemedicine prove that medical equipment will play a greater role in a networked environment.

- The research in China is still in its infancy; for example, the remote network simply stores and transfers medical data in the database rather than truly combining the network with medical equipment. In other countries, although many funds have been invested in research, medical data

is still collected by expensive equipment, and data acquisition and network diagnosis are completed based on a PC and the Internet. Our design will provide a breakthrough in this respect.

- Many design solutions exist today. Systems based on embedded processors such as monolithic, digital signal processors (DSPs), ARM processors, and the Nios<sup>®</sup> II processor are good solutions. We decided to use the Nios II soft-core processor for the following reasons:

- Altera's flexible, efficient system-on-a-programmable-chip (SOPC) solution integrates the Nios II processor, memory, I/O interface, and other functional modules onto a single FPGA to form a programmable system-on-chip. It boasts a flexible design, many available intellectual property (IP) cores, as well as clipping, expansion, and upgrading.

- As an embedded soft-core processor, the Nios II processor features flexibility, high

performance, low cost, and a long life cycle. Additionally, it comes with technical

documentation and examples. Combined with an FPGA, you can develop anything that you

can imagine, which is the key benefit of the Nios II processor and other soft-core CPUs. The

Nios II processor supports μC/OS-II, μClinux, and many other real-time operating systems

(RTOS), a light-weight TCP/IP (LwIP) stack, and zip file system, allowing users to add custom

instructions and custom hardware accelerators, and to migrate customized peripherals and

interface logic seamlessly. These features facilitate user designs while improving

performance.

- Altera is at the forefront of FPGA embedded system development. As soft-core embedded technology evolves, we will have a competitive edge in this field by mastering it early.

Based on these considerations, we decided to focus our design on user terminals that provide convenient, appropriate, operable, and Internet-enabled home telemedicine monitoring equipment for the aging population, young people, and children whose lives rely on technology (e.g., those suffering from accidents, disabilities, and congenital diseases), chronic disease patients, terminal cancer or AIDS patients, and special people (e.g., newborn babies or pregnant women).

## **Function Description**

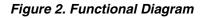

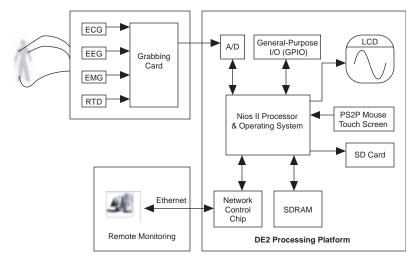

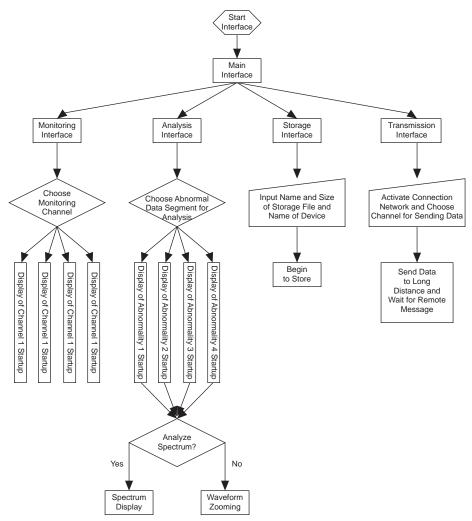

The design offers an effective, convenient medical monitoring solution for home, community, and home-care doctors. Designed mainly for user terminals, the monitoring equipment allows individuals to easily check and analyze their health conditions by themselves and obtain physical information (e.g., biomedical signals such as ECG, EEG, EMG, respiration, temperature, etc). The equipment displays these signals in graphics or waveforms so that individuals know intuitively whether their health indicators are normal. Additionally, the caretaker can make preliminary pathological diagnosis using the equipment's analysis function. The system stores the physical information for subsequent data analysis and processing. With the development of telemedicine, the system can connect patients to medical service (e.g., a hospital, private practitioner, or monitoring center) and deliver the physical information in real time to a remote database or doctor through the network. This feature helps manage medical information databases and provides remote monitoring and diagnosis, allowing individuals to enjoy timely and effective diagnosis without leaving home. See Figure 2.

The design in Figure 2 has the following functionality:

- Multi-way acquisition of biomedical signals—Simulated biomedical signals are collected modularly, e.g., a medical sensor and signal filtering/amplification modulation circuit and separate regulating cards collect different parameters. Because the physical signals frequency bands are below 2 K, we use an analog-to-digital (A/D) conversion chip with a 40 K sampling rate A/D conversion, and reserve a data port for card access.

- *Real-time display of physical information (graphics and data)*—The design uses serial input for data acquisition, saving I/O interface resources and eliminating the synchronization problems caused by parallel input. The collected data is transferred to SDRAM cache by direct memory access (DMA), reducing the CPU load. A display cache is created in SDRAM, while DMA technology transfers data to the liquid crystal display (LCD) for viewing. We designed the A/D acquisition and LCD interface control IP ourselves.

- User-friendly operating interface and diversified processing and analysis functions—We used a 320 x 240 thin-film transistor (TFT) LCD; migrating μC/GUI makes the interface more friendly and attractive. We provide four functional areas: monitoring, analysis, storage, and detection, and

multiple sub-functions simplify the operations. We compiled algorithms for detection, analysis, and processing to the signal characteristics, ensuring high accuracy.

- Multiple functional interfaces (e.g. for network, compact flash (CF) or secure digital (SD) card) to facilitate data storage and transfer—We used an SD card as the storage device and implemented an SD mode. We used the FAT16 file system for data access. A PS/2 interface enables interaction with the monitoring equipment.

- Scalable interface and software upgrades—For hardware, we provided a USB port, serial port, Integrated Development Environment (IDE) interface, and drivers for platform updates. The design adopts a RTOS to support application installation and upgrading.

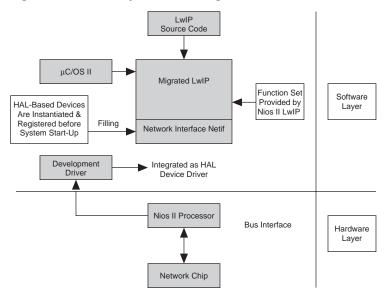

- Embedded web server allows the monitoring equipment to access and receive data via Ethernet— We used the DM9000A network interface chip that has chip control IP that allows us to access the network easily. In the protocol layer, Altera provides a LwIP software component that comprises all protocols required by the network. We used a socket application programming interface (API) to write web server programs that made network communication easy. The design allocates an IP block for the monitoring equipment or uses DHCP. DHCP allows a remote PC to access the monitoring equipment through the Internet to obtain real-time data and parameters and send diagnosis information to local monitoring equipment through the web page's input area, implementing remote monitoring. Additionally, data can be saved to a remote database for management.

## **Performance Parameters**

The following sections provide the design's resource usage and performance parameters.

## Resource Usage

Figure 3 shows the design's system resource utilization given by the Quartus<sup>®</sup> II software. The system has 109.90-MHz  $f_{MAX}$  performance.

#### Figure 3. System Resource Utilization

| Family                             | Cyclone II               |

|------------------------------------|--------------------------|

| Device                             | EP2C35F672C6             |

| Timing Models                      | Final                    |

| Met timing requirements            | No                       |

| Total logic elements               | 8,481 / 33,216 ( 26 % )  |

| Total registers                    | 5569                     |

| Total pins                         | 429 / 475 ( 90 % )       |

| Total virtual pins                 | 0                        |

| Total memory bits                  | 166,784 / 483,840 (34 %) |

| Embedded Multiplier 9-bit elements | 4/70 (6%)                |

| Total PLLs                         | 2/4(50%)                 |

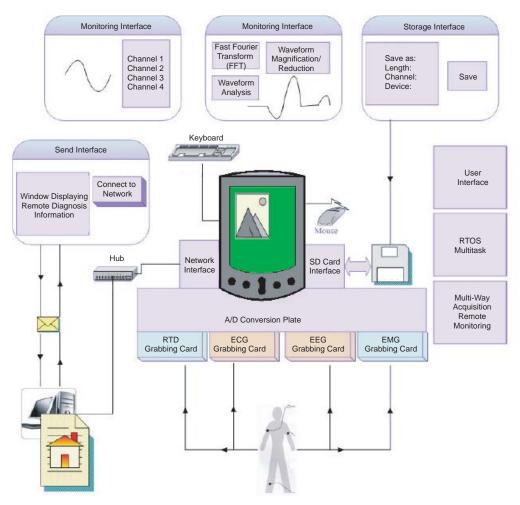

The one-way A/D sampling controller uses 203 logic elements (LEs) and 8,192 memory bits (corresponding to a 512 bytes x 2 cache). It has a sampling frequency in the range of 0 to 1.667 MHz because the TLC549 sampling controller's maximum frequency is 40 kHz and the system's sampling frequency must be 0 to 40 kHz. If the sampling frequency set in software is 1,000 Hz, the output sampling frequency is 999.98 Hz. Figure 4 shows the A/D chip sampling rate.

Figure 4. A/D Chip Sampling Rate

The system software uses 3,046 Kbytes for storage.

## **Design Performance Parameters**

The following sections describe the performance parameters of the design.

## **Front-End Acquisition Board**

Table 1 shows the pre-amplifier channel bandwidth test. The pre-amplifier gain is stable between frequency bands of 1 to 1 kHz, i.e., the channel bandwidth is  $\geq$  1 kHz.

Table 1. Pre-Amplifier Gain Changes with Frequency

| f (Hz)          | 1    | 5    | 10   | 20   | 50   | 100  | 200  | 500  | 1,000 |

|-----------------|------|------|------|------|------|------|------|------|-------|

| G (Vpp = 10 mV) | 12.1 | 12.4 | 12.3 | 12.4 | 12.0 | 12.1 | 12.1 | 12.1 | 12.1  |

Table 2 shows the amplifying power of the amplifier for different signals. At 20- and 50-Hz frequencies, the amplifier gains are stable when the input signal amplitude changes.

Table 2. Pre-Amplifier Gain Changes with Input Signal

| Vpp (m | ιV)       | 40   | 60   | 80   | 100  | 120  | 150  | 300  | 400  | 800  |

|--------|-----------|------|------|------|------|------|------|------|------|------|

| G      | f = 20 Hz | 11.9 | 12.3 | 12.4 | 12.6 | 12.5 | 12.7 | 12.5 | 13.0 | 13.3 |

|        | f = 50 Hz | 11.9 | 12.3 | 12.4 | 12.9 | 12.7 | 12.9 | 12.4 | 13.1 | 13.3 |

Table 3 shows the trapper's trap feature test. The attenuation degree is increased by compromising trap impedance, i.e., a proper point is adjusted to obtain the attenuation and trap impedance.

Table 3. Change of 50-Hz Trapper with Frequency

| f (Hz)          | 1   | 10  | 20  | 40  | 45  | 47  | 48  | 49  | 50  | 51  | 52  | 53  | 55  | 60  | 80  |

|-----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| G (Vpp = 50 mV) | 6.4 | 6.4 | 6.8 | 4.5 | 2.8 | 2.0 | 1.5 | 1.0 | 0.6 | 0.9 | 1.3 | 1.6 | 2.4 | 4.3 | 6.1 |

### **SD Card Parameter Test**

The test uses 100 16-bit data for reading/writing text files, which takes 40 ms. Assuming that the frontend data sampling is 2 kHz and 2,000 data points are collected every second, the storage time would be  $(2,000/100) \times 40 \text{ ms} = 800 \text{ ms}$ . The test result shows that the collected data is not lost. See Table 4.

| Operation                   | Function                                              |

|-----------------------------|-------------------------------------------------------|

| File system start/exit      | FS_EXIT(), FS_INIT                                    |

| Open/close file             | FS_FCLOSE(), FS_FOPEN()                               |

| Read/write file data        | <pre>FS_FREAD(), FS_FWRITE()</pre>                    |

| Locate file                 | FS_FSEEK(), FS_FTELL()                                |

| Remove file/file directory  | FS_REMOVE()                                           |

| Create/close file directory | <pre>FS_MKDIR(), FSCLOSEDIR()</pre>                   |

| Open/read/locate directory  | <pre>FS_OPENDIR(), FS_READDIR(), FS_REWINDDIR()</pre> |

Table 4. SD Card File Operation Functions

## **Network Speed Test**

We set the monitoring equipment's IP address to 192.168.220.236 in the test using the Linkwan.com web site test tool. Figure 5 shows the test result.

#### Figure 5. IP Address Test

| 网站。                    | 反应速度测试 |

|------------------------|--------|

| 网站                     | 反应时间   |

| http://192.168.220.236 | 0.11秒  |

We tested the operation of the built-in ping command as shown in Figure 6.

### Figure 6. Ping Command Test

## **ECG Signal Detection Result**

Table 5 shows the R-wave detection results and Table 6 shows the data compression result. The data source is the MIT/BIT ECG database, with 250-Hz sampling, 8-bit quantification, and four signal groups collected for detection. The ECG detection algorithm's average R-wave false detection rate is

0.58%, the data compression ratio is as high as 13.75 times, and the correlation coefficient (CC) reaches 98.9%. The indicators are generally at a high level.

Table 5. R-wave Detection Result

| Signal  | Total Heart<br>Rate | False Accept<br>Rate | Undetected | False<br>Detected<br>Heart Rate | False<br>Detection<br>Rate (%) |

|---------|---------------------|----------------------|------------|---------------------------------|--------------------------------|

| Sddb-30 | 1,545               | 4                    | 1          | 5                               | 0.32                           |

| Sddb-32 | 2,013               | 6                    | 7          | 13                              | 0.66                           |

| Sddb-35 | 3,326               | 15                   | 14         | 29                              | 0.87                           |

| Sddb-37 | 2,111               | 4                    | 6          | 10                              | 0.47                           |

Table 6. Data Compression Result

| Signal  | CR Compression Ratio (%) | PRD (%) | Correlation Coefficient (%) |

|---------|--------------------------|---------|-----------------------------|

| Sddb-30 | 19                       | 7.3     | 99.7                        |

| Sddb-32 | 11                       | 16      | 98.8                        |

| Sddb-35 | 12                       | 23      | 97.9                        |

| Sddb-37 | 13                       | 13      | 99.2                        |

## **Design Architecture**

The monitoring equipment mainly consists of three modules (see Figure 7):

- Front-end collection and modulation

- Signal processing, storage, and transfer platform

- Remote monitoring

#### Figure 7. System Structure

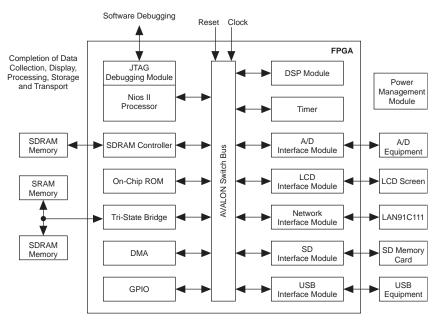

The hardware platform is the Development and Education (DE2) board, which contains the Altera<sup>®</sup> Cyclone<sup>®</sup> II EP2C35F672C6 FPGA. The hardware integrates the Nios II soft-core processor, memory, IP functions, and I/O ports on a single FPGA via SOPC technology. Peripheral hardware, including the data acquisition module, network, LCD screen, touch screen/keyboard, USB/SD memory, etc., are extended with a scalable I/O interface to facilitate system upgrades. Figure 8 shows the hardware platform.

### Figure 8. SOPC Hardware Platform

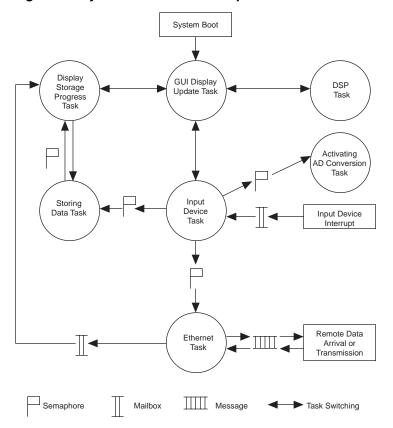

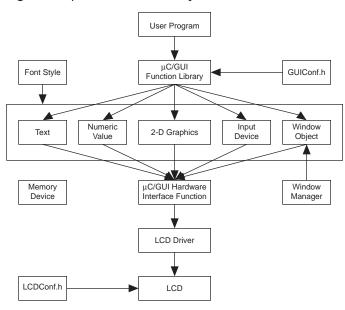

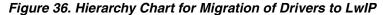

Because our hardware platform is designed using SOPC concepts, the Nios II system is written using a hardware abstraction layer (HAL) driver, including the A/D conversion control IP core, LCD control core, network control IP, SD card control core, PS2 IP, etc. For multi-tasking, we used  $\mu$ C/OS-II for system dispatching. Additionally, we migrated  $\mu$ C/GUI and  $\mu$ C/FS as our graphical interface and file system, respectively. The LwIP protocol stack is a part of the software layer, and performs TCP/IP network communication. Other applications include a web server, operating interface, signal processing, fast Fourier transform (FFT) algorithm, and data compression. Figure 9 shows the software layer structure.

Figure 9. Software Layer Structure

| LCD Operating Inte<br>Application | erface Data                     | a Compression/Signal<br>Data Analysis/Data / |           |                                | Web Server<br>Application |  |

|-----------------------------------|---------------------------------|----------------------------------------------|-----------|--------------------------------|---------------------------|--|

| μC/GUI                            |                                 | μC/FS                                        |           | LwIP Network<br>Protocol Stack |                           |  |

|                                   | Ì                               | μC/OS-II RT0S                                |           |                                |                           |  |

|                                   |                                 | HAL API                                      |           |                                |                           |  |

| LCD Driver                        | AD Conversion<br>Control Driver | SD Card Driver                               | Network D | river                          | Input Device<br>Driver    |  |

## **Design Methodology**

This section describes our design methodology.

## **Biomedical Signal Regulation Card Design**

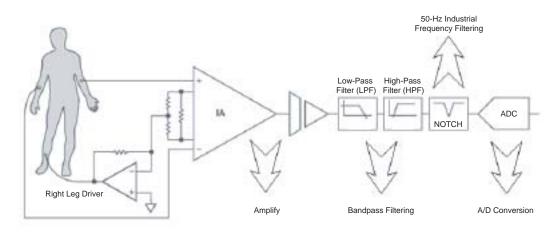

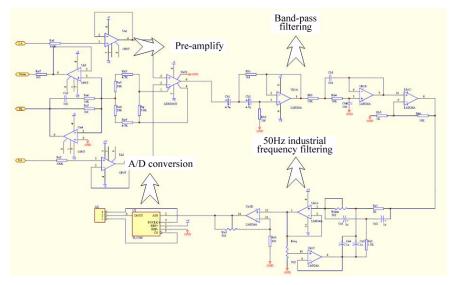

The biomedical signals are collected modularly, including the medical sensor, signal filtering amplifying modulation circuit, and A/D sampling circuit. The modulation circuit selects different filters and the amplified circuit according to the spectrum and scope of different biomedical signals. Using ECG as an example, the signal is amplified via the pre-amplification block, including a right leg driver to suppress common mode interference, a shield wire driver to eliminate lead wire interference, and the tenfold set gains.

We designed the pre-amplification block using the Analog Devices AD620 medical amplifier. The AD620 device is based on a modification of the classic three operational amplifier approach and is integrated using a co-phase differential amplifier in parallel. The AD620 device has a wide power supply range ( $\pm 2.3$  V to  $\pm 18$  V), small size, and low power (it uses only a 1.3 mA maximum supply current), making it a good fit for low-voltage, low-power applications. Other advantages include a high common-mode rejection ratio, sound temperature stability, amplified bandwidth, and low noise. The amplified signal is further magnified using filtering and a 50-Hz trap filter. The post gain is set as 1 to 100. Because the maximum ECG signal is several mV and the A/D conversion input signal is over 1 V, the total gain is set as 1 to 1,000. Filtering uses a voltage-controlled voltage source second-order high (low) pass filter to eliminate signals interference such as myoelectricity beyond 0.05 to 100 Hz, as well as other high-order industrial frequency harmonics. Additionally, we used an active twin-T band-stop filtering circuit to curb the 50-Hz industrial frequency interference.

The A/D sampling chip is the Texas Instruments (TI) 8-bit serial TLC549 device. It uses a serial peripheral interface (SPI) to provide collection control and data transmission using three wires. It provides an on-chip system clock that typically operates at 4 MHz, as well as a software/hardware controlled circuit with a conversion time of less than 17 µs and a sampling rate of 40 kilosamples per second (KSPS). With a differential voltage reference, the TLC549 device can measure a minimum value of 1,000 mv/256, i.e., 8-bit resolution can be obtained without amplifying the 0- to 1-V signal. Figure 10 shows the ECG signal regulating card structure and Figure 11 shows the circuit diagram.

Figure 11. ECG Collection Circuit Diagram

## SOPC Hardware Platform Design

We designed the hardware platform based on the Nios II processor. For our work, we first implemented the IP design, such as the A/D conversion control, LCD control, and data storage/transfer using a custom peripheral.

## A/D Conversion Control IP Design

The A/D module design prevents the front-end signals from distortion and loss and deal synchronizes the data because of the multi-channel acquisition.

## A/D Sequence Control Module

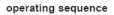

The system's A/D conversion chip is the TI TLC549 (TLC548) device, which is a low-cost, highperformance, 8-bit A/D converter. It implements A/D conversion using an 8-bit switched-capacitor successive-approximation approach. With a conversion speed of less than 17  $\mu$ s, the TLC549 device can easily connect to various microprocessors using a three-wire serial interface to form various low-cost test and control application systems. With a differential voltage reference, the TLC549 device can measure the minimum value of 1,000 mv/256, i.e., we can obtain 8-bit resolution without amplifying the 0- to 1-V signal. Sequence control is generated according to the sequence diagram shown in Figure 12.

### Figure 12. TLC549 Sequence Diagram

According to the sequence, the following tasks are performed when eight external clock signals are input at the TLC549 device's I/O clock: read the previous A/D conversion result, sample and reserve the input analog signal converted currently, and initiate A/D conversion.

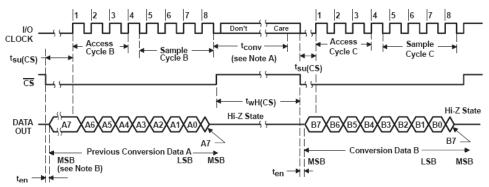

To implement the TLC549 analog controller in the FPGA, we designed the simulation with a Verilog HDL control state machine as shown in Figure 13:

Figure 13. State Machine Sequence

din is the serial input of data collected, and the clock is obtained through frequency division coefficient. fsm is the sampling control clock to adjust sampling speed as required.

#### **Double-Buffered Operating Technology**

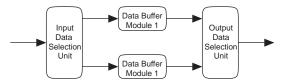

Because A/D sampling is short, it is impractical to query or read data with interrupts. Therefore, the buffer design must reduce the interruption time by temporarily storing the converted data for N times in the buffer memory. To collect data continuously and correctly implement a seamless buffer, we use a ping-pong operation structure with double-buffer storage that takes advantage of the FPGA's design flexibility. The ping-pong operation is a handling technique for the data stream (see Figure 14). The data buffer module can be any storage unit and in this design we use dual-port RAM (DPRAM).

Figure 14. Ping-Pong Operation

During ping-pong operation, the input data streams are distributed to two data buffer areas through the input data selection unit. The data buffer module can be any storage module, and the common storage units include DPRAM, single-port RAM (SPRAM), FIFO, etc. In the first buffer period, the input data stream is cached into data buffer module 1. In the second buffer period, the input data stream is cached into data buffer module 2 using the input data selection unit switch while the first period data in data buffer module 1 is output through the output port and the output data selection unit. In the third buffer period, the input data stream is cached into data buffer module 2 is switched by the output data selection unit while the second period data in data buffer module 2 is switched by the output data selection unit and output via the output port for operation. The process repeats as required.

The ping-pong operation's unique feature is the collaborative switching of the input and output data selection units according to a meter, which sends the buffered data streams to the data stream processing unit for operation without pausing. The ping-pong operation module is an independent function and the input and output data streams are continuous at the sides of the module; therefore, the design can process data streams in the form of a pipeline. Ping-pong operation is usually applied in a pipeline algorithm for seamless data buffering and processing.

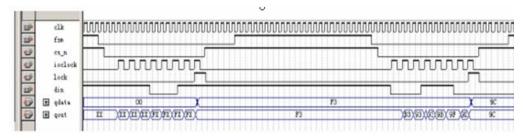

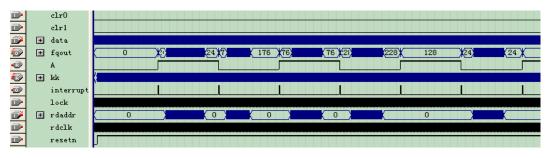

This design implements a data cache by alternatively storing an A/D sampling sequence controller into two 512-byte DPRAM blocks. When DPRAM1 is full, the data is stored in DPRAM2 with one interrupt so that the system has enough time to move the data out of DPRAM1 when the controller writes data into DPRAM2. Figure 15 shows the DPRAM buffer system timing diagram.

Figure 15. DPRAM Buffer System Timing Diagram

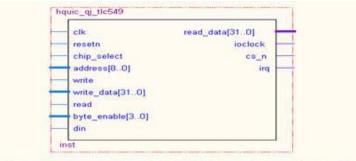

#### **IP** Design

The final IP core in the A/D sampling module includes an A/D conversion sequence controller, a double-buffer ping-pong operation module, a control register such as a sampling clock frequency division controller, and a bus control signal. Figure 16 shows the A/D conversion control IP core structure, which can connect directly to the Avalon<sup>®</sup> bus and can be added to the system if necessary. Four cores are added to the system.

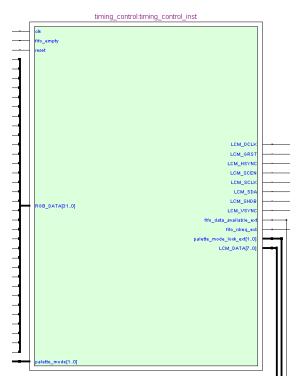

Figure 16. AD Conversion Control IP

AD data conversion control IP with double buffer technology and DPRAM

Each IP core has an independent double buffer and control register, which work in parallel. Control registers include a sampling clock controller (FSAMPLE), A/D-enabled control (EN\_AD), etc. The sampling speed is controlled by setting the value of the sampling clock controller. For example, if we want to perform 10-kHz sampling for the analog signal with a 5-MHz control clock, the core just writes 10,000 in FSAMPLE and then a 1 in EN\_AD to initiate the A/D conversion.

#### **DMA Transmission**

Our design uses the DAM core to move data blocks from DPRAM to SDRAM in the A/D conversion IP core. This process needs to write control instructions into the DMA control register to initiate the data transmission process. The status, read address, write address, length, and control registers require initialization. The DAM operation is initiated using the system's DAM subprogram. In the HAL API, the party with an auto-incremental address opens a receiving or sending channel and configuration address; the fixed-address party sets the alt\_dma\_rxchan\_ioctl() parameters (using ALT\_DMA\_RX\_ONLY\_ON or ALT\_DMA\_TX\_ONLY\_ON) and the configuration address. For data transmission from DPRAM to the SDRAM, that is, when both source and destination are in auto-incremental address mode, we use the following DMA data transmission code:

```

tx = alt_dma_txchan_open("/dev/dma_0");

dma_res = alt_dma_txchan_send(tx, ad_buf, 32, NULL, NULL);

// ad_buf is the source address

rx = alt_dma_rxchan_open("/dev/dma_0");

dma_res = alt_dma_rxchan_prepare(rx, ad_buf, 32, dma_done, NULL);

// ad_buf is the destination address, dma_done() is the call back function

// employed upon the completion of DMA.

```

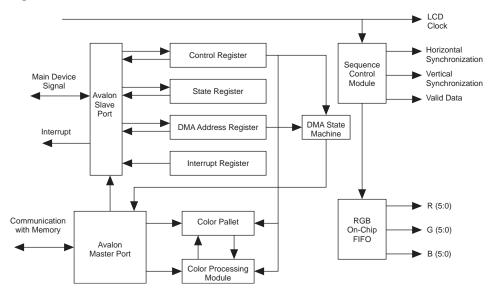

## LCD IP Design

Our design requires a display device to show the collected signals and data waveforms in a format that is easy to understand. We used an LCD screen with the Terasic TRDB\_LCM expansion board. The board has a Toppoly TD036THEA1 compact LCD module, can process an 8-bit (RGB or YUV) digital signal, and supports TSC and PAL sequences. It has a three-wire register control for display and function selection as well as embedded contrast, brightness, and rectification modules. It supports band color filtering 960 x 240 (TH mode, three primaries (red, green, and blue) virtualization, and YUV input). The expansion board is connected to the DE2 board's GPI0\_0 expansion port.

We use progressive scanning, and the LCD clock is 25.175 MHz. The design uses a three-wire LCM to configure the IP. The IP core's main function is to compile the state machine according to the control sequence in the data sheet and deliver configuration data. Figure 17 shows the TRDB\_LCM block.

### Figure 17. I2S\_LCM Block

|   | I2S_LCN      | /I_Config:u4                     |  |

|---|--------------|----------------------------------|--|

| _ | iCLK<br>iRST | I2S_SCEN<br>I2S_SCLK<br>I2S_SDAT |  |

The LCD module does not have a display controller, so we designed it independently with Verilog HDL. The controller supports multiple color modes, including 18, 16, and 8 bpp, and self-defined mode. The image memory uses an on-chip FIFO buffer, which is adjustable according to design needs. A 256-color look-up table also adopts on-chip RAM. The image information can be read automatically from memory with DAM using the Avalon bus's main module transmission port. Figures 18 and 19 show the system.

Figure 18. LCD IP Core Structure

### Figure 19. LCD IP Core RTL

The LCD core has four modules: the interface module, memory module, color conversion module, and sequence module.

The interface module operates the controller and reads the state. It contains a control register, state register, DMA address register, and interrupt register. See Table 7.

| A1-A0 | Register             | Read/write   | Description/Register Bit                    |              |   | r Bit   |   |   |

|-------|----------------------|--------------|---------------------------------------------|--------------|---|---------|---|---|

|       |                      |              | 315                                         | 4            | 3 | 2       | 1 | 0 |

| 0     | Control register     | Read & write |                                             | EIRQ PMODE E |   | EDMA    |   |   |

| 1     | State register       | Read & write | Status Inquiry                              |              |   |         |   |   |

| 2     | DMA address register | Read & write | Write the start address of DMA transmission |              |   | mission |   |   |

| 3     | Interrupt register   | Read         | Clear interrupt                             |              |   |         |   |   |

Table 7. LCD Controller Registers

The control register's EDMA initiates the DMA, PMODE selects the color pallet mode (18, 16, and 8 bpp, and self-defined), and EIRQ enables interrupts. The state register queries the interrupt state. The DMA address register sets and queries the DMA start address. The interrupt register clears interrupts.

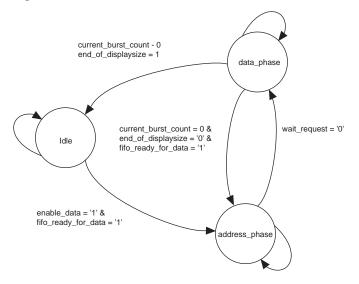

The memory module reads the SDRAM's FRAMEBUFFER data independently into an on-chip FIFO in DMA mode using a state machine that reads/writes the Avalon master port. Based on the sequence, the state machine has three states: idle, address, and data. In idle state, it waits for the DMA start-up signal and initializes the module transmission and DMA start address number. When the DMA enable signal is initiated and the on-chip FIFO buffer is idle, it jumps to the address state. In address state, the wait signal on the wait bus is cancelled to enter a data read state. In data read state, the read signal begins to

read the SDRAM address data, and the module counter reduces by 1 for each consecutive data block. It returns to address state after reading a data block and adds the address automatically. It returns to idle state after reading a frame of data and waits for the transmission of the next frame. See Figure 20.

Figure 20. DMA State Machine

The color conversion module converts the read data according to four color modes. The 8 bpp and selfdefined modes require a color look-up table because they have insufficient colors. The self-defined mode can preset the color pallet's address manually to define the color output.

The sequence module is compiled strictly according to the sequence of the LCD. The LCD clock is 25 MHz. The FIFO data output is initiated by controlling the data enable signal, and is displayed with a progressive scan. Meanwhile, the design must check whether there is data in the FIFO buffer before the data effective signal arrives to decide whether to read and transmit data. The color pallet mode is set and locked during frame transmission to avoid errors. Different read time periods are determined according to the bpp mode: BPP\_18 must be read every time, BPP\_16 is read every two times, and BPP\_8 is read every five times.

We verified that the core outputs data and synchronous signals are stable, and sets display mode and RGB data bits through the register. Figure 21 shows the LCM analog sequence signal output to the DE2 board's GPIO\_0 expansion port.

|       | GPI0_0[18] "result<br>GPI0_0[19] "result<br>GPI0_0[20] "result<br>GPI0_0[21] "result<br>GPI0_0[22] "result<br>GPI0_0[23] "result |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------|--|

| 00000 | GPIO_0[24] "result<br>GPIO_0[25] "result<br>GPIO_0[26] "result<br>GPIO_0[27] "result<br>GPIO_0[28] "result<br>GPIO_0[29] "result |  |

|       | GPIO_0(30)~result<br>GPIO_0(31)~result<br>GPIO_0(32)~result<br>GPIO_0(33)~result                                                 |  |

Figure 21. Analog Sequence of LCM Signal Output to GPIO\_0 of DE2 Expansion Port

## **SD Card Interface Design**

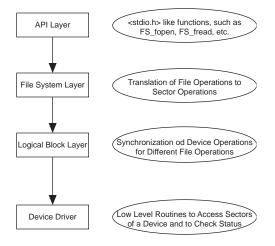

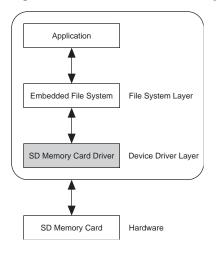

One of the design's functions is to store the monitoring data. We use the DE2 board's SD card interface for large-volume data storage. The highly integrated SD card flash memory has serial and random access capabilities. It allows access through the specified serial interface with optimized speed and reliable data transmission, and we can stack several externally connected cards together. The interface completely complies with the SD card system standard defined by the SD card system specification, which is the latest consumer standard. The SD card clock is generated by the internal clock generator, and the interface driver unit synchronizes the external clock's DAT and CMD signals with the internal clock. The SD card has two communication protocols: SD and SPI. Comparing the two protocols, the biggest advantage of SD is that it has fast reads/writes, up to a theoretical 25 Mbytes/second for a single data line. The SD card interface in our system uses a single data line, DATA0. Three parallel I/O (PIO) IP blocks are used in the SOPC design as SDATA, SCLK, and SCMD SD card single data lines.

We compiled the SD card protocol in software and migrated the file system to save FPGA resources without any impact on the read/write speed. See "Software Platform Design" on page 356 for details.

## HAL Network Driver-Based Design

The Nios II system takes HAL as a BSP to provide a unified peripheral interface in the embedded system. The HAL device driver abstraction, the main service provided by the HAL system library, is highly integrated into the SOPC design, allowing later software development to facilitate development and updates without hardware impact. The DM9000A-based HAL device driver development has two steps: designing the DM9000A read/write driver and migrating the DM9000A driver in HAL-based driver mode.

#### **DM9000A Read/Write Driver**

The DM9000A device is an integrated 10/100 Mbyte adaptive Ethernet control chip on the DE2 board. It has low cost and fast speeds, and features a common processor interface, 10/100 Mbyte adaptive, and 16 Kbit static access memory. Its simple design allows easy development of software drivers for different systems.

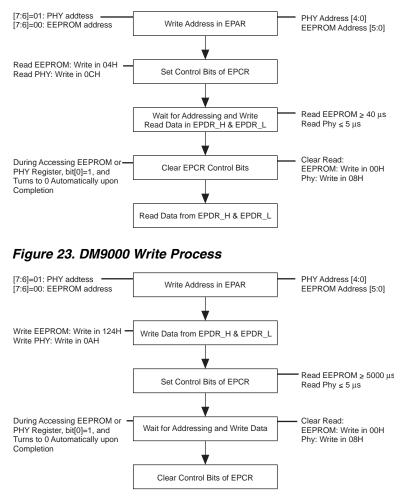

The DM9000A device cannot directly access the in-chip registers, but it can read/write using the data and index ports, which are controlled by the CMD pin. When CMD is high, it is a data port, and when CMD is low, it is a control port. The process to read/write any register is as follows:

- 1. Enable the DM9000A device by setting AEN and SA7 low, and SA8 and SA9 high (this step is generally done in hardware without setting it in software).

- 2. Set the CMD pin low using software.

- 3. Input the register location to be read/written on the index port.

- 4. Set CMD pin high.

- 5. Input/output the register data to be read/written at the material port. See Figures 22 and 23.

#### Figure 22. DM9000 Read Process

#### **Develop DM9000A HAL Network Device Driver**

Because the DM9000A device provides a complete bus interface, we need the Avalon bus and DM9000A interface logic in SOPC Builder. The DM9000A device communicate with the Nios II processor as an Avalon slave. Creating a HAL device driver includes creating device instances and registering the character device.

By referring to the HAL device driver development documentation and focusing on the lightweight IP (LwIP) driver structure, we defined the following structure DM9000A alt\_dev structure:

```

typedef struct

{

alt_lwip_dev_list lwip_dev_list;

int base_addr;

int irq;

```

```

u_char hwaddr[6];

int index_offset;

int data_offset;

int dm9k_tx_space;

int dm9k_linked;

sys_sem_t arp_semaphore;

sys_sem_t tx_semaphore;

} alt_avalon_dm9k_if;

```

When the Nios II processor starts running, the device is initialized in alt\_sys\_init(), allowing the program to identify the driver.

```

#define ALTERA_AVALON_DM9K_INSTANCE(name, dev) \

/*instantiate device*/

alt_avalon_dm9k_if dev = \setminus

{\

{\

ALT_LLIST_ENTRY, \

{\

0,\

name##_NAME,\

alt_avalon_dm9k_init, \

},\

},\

pr

alt_avalon_dm9k_rx, \

name##_BASE, \setminus

name##_IRQ,\

{ 0x00, 0x90, 0x00, 0xAE, 0x00, 0x01}, \

0, 1, 2

}

#define ALTERA_AVALON_DM9K_INIT(dev)alt_lwip_dev_reg(dev) //initialize

//devices, register in HAL.

```

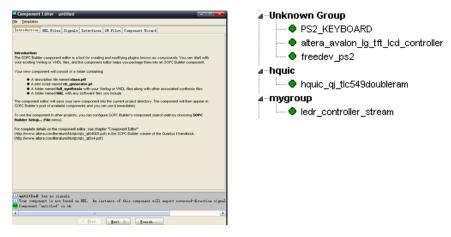

## **SOPC Builder**

The Quartus II software's SOPC Builder integrates a hardware system in an FPGA, including writing the CPU, memory, interface IP blocks, timer, and Avalon bus in a hardware description language, and presenting it in the form of an IP block. Using the DE2 development board and considering the design functionality, we created the SOPC system.See Figures 24 and 25.

|                                                                                 | ONios II/e                                                                                   | ONios II/s                                                                                                                                                 | ONio:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | s II/f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nios II<br>Selector Guide<br>Family: Cyclone II<br>f <sub>ermien:</sub> 100 MHz | RISC<br>32-bit                                                                               | RISC<br>32-bit<br>Instruction Co<br>Branch Fredict<br>Mardvare Hulti<br>Mardvare Divid                                                                     | RISC<br>32-bit<br>ion Branch J<br>ply Mardware<br>Barrel<br>Barrel<br>Bart Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | tion Cache<br>Frediction<br>9 Multiply<br>9 Bivide<br>Shifter<br>ache<br>8 Branch Frediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Performance at 100 M                                                            | Hr Up to 9 DMIPS                                                                             | Up to 50 DMIPS                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DI DMIPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Logic Vange                                                                     | 600-700 LEs                                                                                  | 1200-1400 LEs                                                                                                                                              | 1400-100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| lenory Vange                                                                    | Two MiKs                                                                                     | Two DiKs + cache                                                                                                                                           | Three Di                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Us + cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

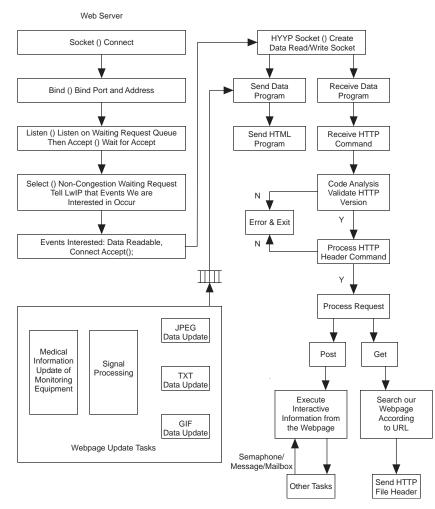

|                                                                                 |                                                                                              |                                                                                                                                                            | ğent ≥ _ Einisl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |