### Power Distribution Network Design for Stratix IV GX and Arria II GX FPGAs

Transceiver Portfolio Workshops 2009

© 2009 Altera Corporation—Public

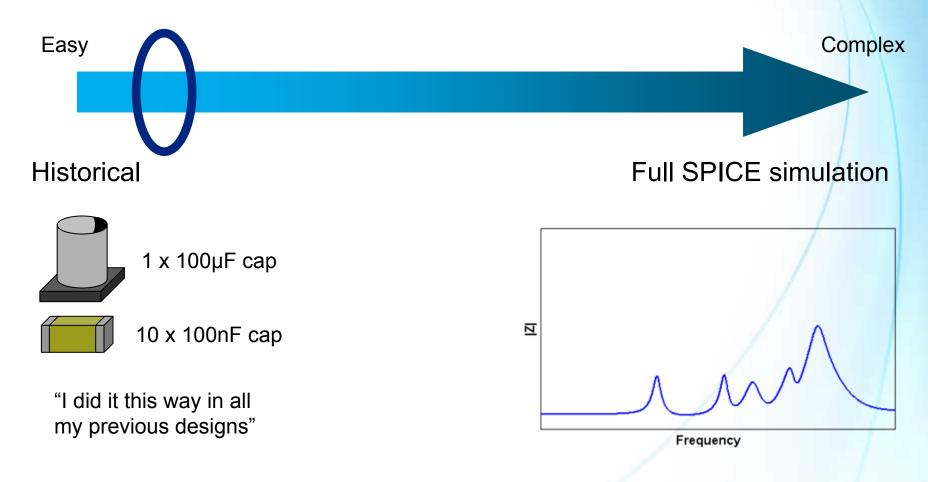

### Question – What is Your PDN Design Methodology?

© 2009 Altera Corporation—Public

#### Agenda

- Power integrity issues

- Challenges of 40-nm PDN design and Altera innovations to help

- What is the PDN?

- PDN design and decoupling schemes

- Power distribution network design

- Altera's PDN design tool flow

- Summary

© 2009 Altera Corporation—Public

### **Common Power Integrity Issues**

- Power integrity issues can result in:

- Increased jitter

- Poor timing results (decreased slew rate)

- Device brown-out and metastability

- Logic errors

- EMI (electromagnetic interference) problems

- Power integrity issues can be:

- Difficult to diagnose

- Be found late in design cycle or post-deployment

#### Need a power distribution network design methodology

© 2009 Altera Corporation—Public

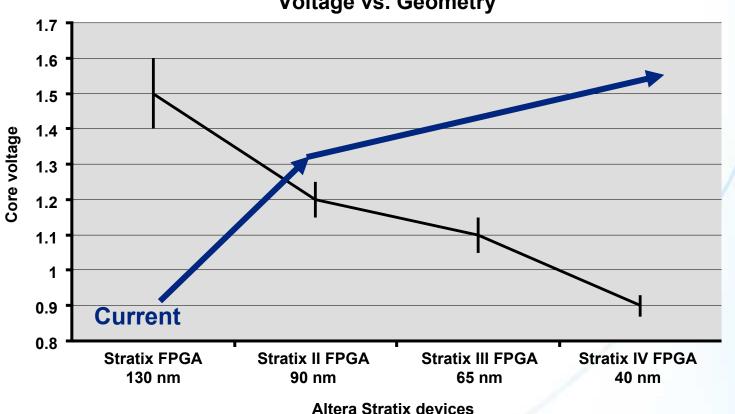

## **Technology Challenges**

Larger densities and lower voltages with less noise margin create challenges for power design

Voltage vs. Geometry

© 2009 Altera Corporation—Public

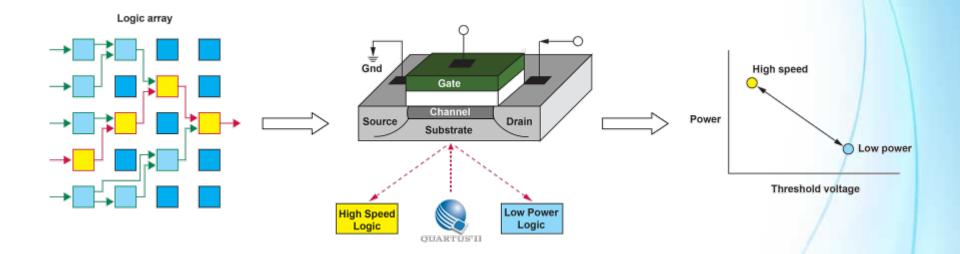

### Programmable Power Technology (PPT) for Stratix III and Stratix IV FPGAs

#### Quartus II software automatically adjusts transistor threshold voltage for low power and high performance

Note: A very simplistic "model" of Programmable Power Technology. Actual implementation varies and is patented.

© 2009 Altera Corporation—Public

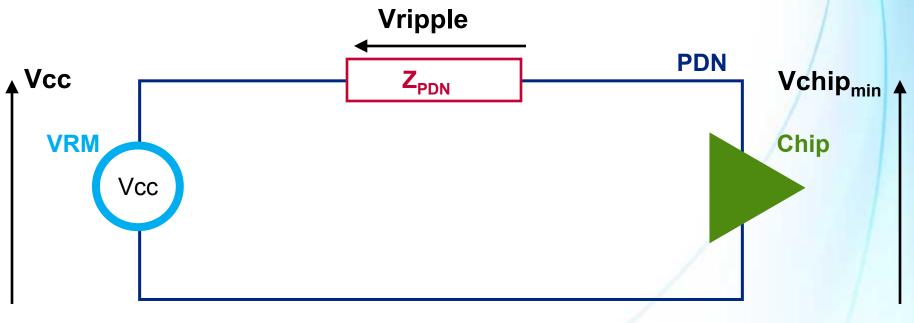

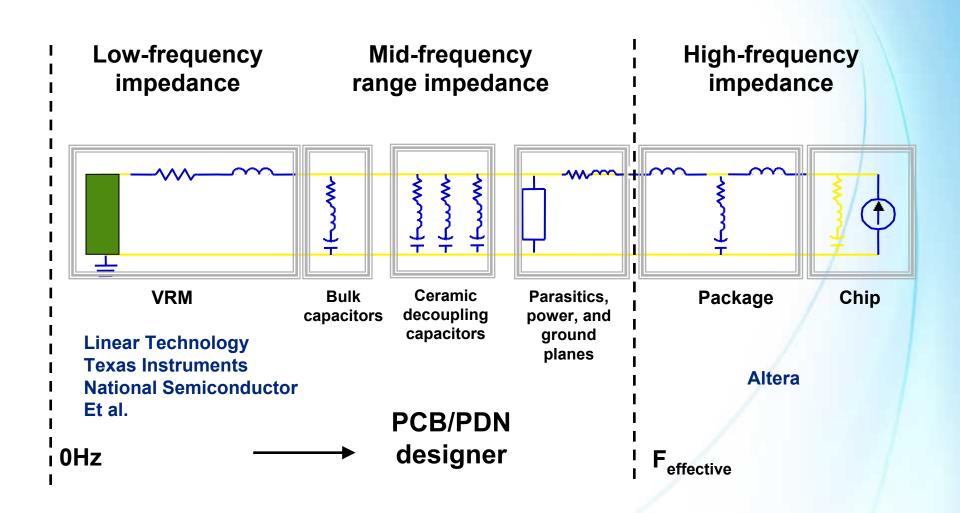

### **Role of the PDN**

Distributes clean power to each device from the voltage regulating module (VRM) to the power rails of the chip

– Keep ripple noise (rail collapse) < spec (typically 5%)</p>

Provides return path for I/O signals

#### Vcc - Vripple ≥ Vchip<sub>min</sub>

© 2009 Altera Corporation—Public

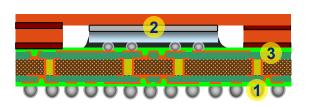

# **Simplified Model of a PDN**

© 2009 Altera Corporation—Public

# PDN and Decoupling Schemes

© 2009 Altera Corporation—Public

ALERA

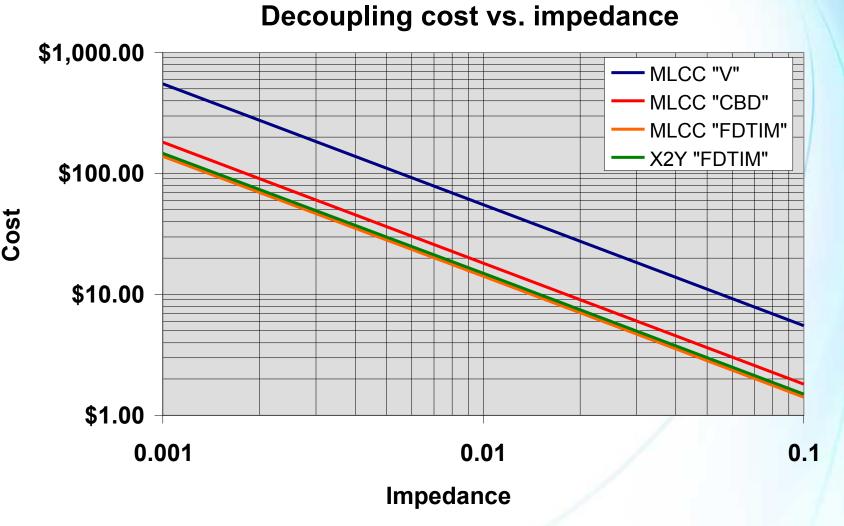

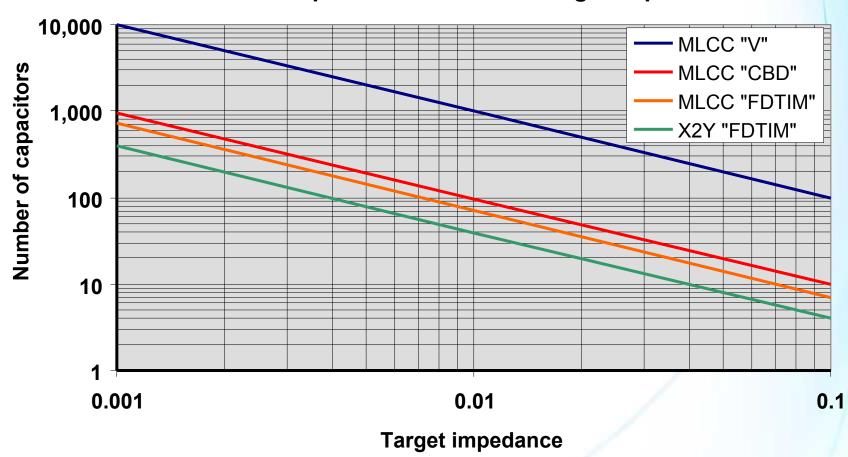

# **Different Schemes for Decoupling**

- Frequency domain target impedance methodology (FDTIM) or multi-pole (MP)

- Good: Least number of capacitors, very stable, and low cost

- Bad: Requires analysis of the network and can require many different capacitor values

- Capacitors-by-the-decade (CBD)

- Good: Less capacitor types than FDTIM and fewer capacitors than Big-V

- Bad: Produces a more unstable solution than FTDIM with more capacitors, requires some analysis

- Big-V

- Good: Least number of different capacitors, requires least amount of analysis

- Bad: Requires the most amount of capacitors, making it inefficient, extremely costly, and possibly unstable

- Distributed matched bypassing (DMB)

- Good: Most stable, requires less capacitors than Big-V or CBD

- Bad: Requires the most analysis with costly embedded PCB resistors, capacitor value is locked per capacitor pad

<sup>© 2009</sup> Altera Corporation—Public

### **Decoupling Cost for Each Scheme**

© 2009 Altera Corporation—Public

### **Capacitors Needed for Decoupling Scheme**

#### Number of capacitors needed vs. target impedance

© 2009 Altera Corporation—Public

# Power Distribution Network Design

ADERA.

Altera's PDN Design Tool Flow

© 2009 Altera Corporation—Public

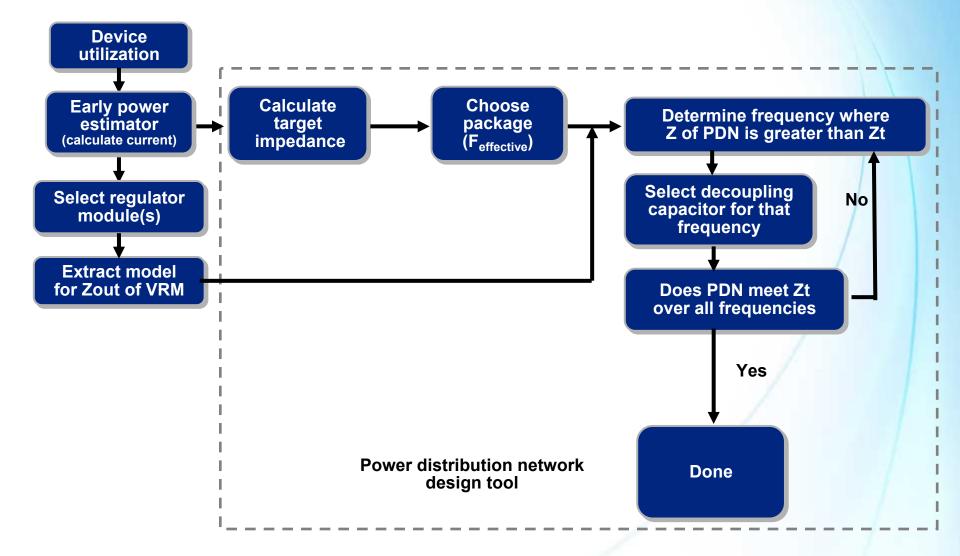

### **Power Distribution Network Design Flow**

© 2009 Altera Corporation—Public

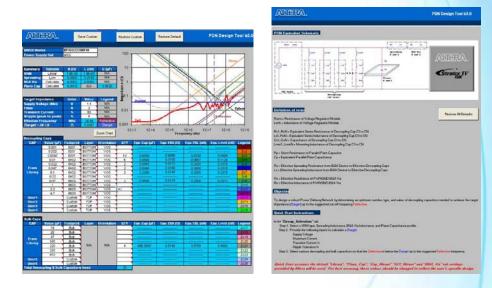

# Altera's Power Distribution Network Design Tool

- Excel spreadsheet tool

- You supply:

- Rail current

- VRM choice

- Package choice

- PCB specification

- Stack up, via size, capacitor outline

- Spreading inductance

- You select:

- Capacitor values and quantity

- Tool shows you:

- Impedance plot over frequency

#### Robust, low-cost PDN suited to your design

© 2009 Altera Corporation—**Public**

# **PDN Design Tool Flow**

#### Stratix IV GX FPGA – VCC supply example

| SIVGX Dev                 | ice         | EP4SGX230KF40    |         |            |  |

|---------------------------|-------------|------------------|---------|------------|--|

| <b>Power Sup</b>          | ply Rail    | VCC              |         |            |  |

|                           |             |                  |         |            |  |

|                           |             |                  |         |            |  |

| Summary                   | Options     | R (Ω)            | L (nH)  | C (μF)     |  |

| VRM                       | Switcher    | 1.0E-03          | 2.0E+01 | N/A        |  |

| Spreading                 | Low         | 0.0005           | 0.0150  | N/A        |  |

| BGA Via                   | Calculate   | 0.0002           | 0.0261  | N/A        |  |

| Plane Cap                 | Calculate   | 0.0019           | N/A     | 0.0630     |  |

|                           |             |                  |         |            |  |

|                           |             |                  |         |            |  |

| Target Imp                | edance      | Units            | Value   | Legend     |  |

| <b>Supply Vol</b>         | tage (Min)  | V                | 0.9     | N/A        |  |

| l max                     |             | Α                | 3       | N/A        |  |

| Transient C               | Current     | %                | 50      | N/A        |  |

| Vripple (pe               | ak-to-peak) | <mark>%</mark> 3 |         | N/A        |  |

| Effective Fi              | requency    | MHz              | 24.84   | Feffective |  |

| <b>Ztarget =</b> $\Delta$ | V / ΔI      | Ω                | 0.0180  | Ztarget    |  |

#### PDN tool setup

- Select device (package)

- With BGA, via and plane spreading generates f<sub>effective</sub>

- Select voltage regulator module (VRM)

- Type

- Select plane capacitance

- Type

- Supply rail

- Voltage

- Ripple voltage as %

- See appendix

- Compute maximum supply current

- Use early power estimator value

- Or use Quartus II PowerPlay power analyzer maximum transient current to adjust transient current %

© 2009 Altera Corporation—Public

### **Calculating Target Impedance**

- Altera target impedance (Zt) is calculated for each rail by dividing the allowed voltage deviation by the dynamic current drawn by the device

- The dynamic current is calculated to be 50% of the maximum current drawn, estimated from EPE

$$Z_{Target} = \left(\frac{V_{rail} \times \% \_ripple}{\frac{1}{2}I_{MAX}}\right) = \left(\frac{V_{ripple}}{\frac{1}{2}I_{MAX}}\right)$$

PowerPlay power analyzer in Quartus II software provides the maximum dynamic current

$$Z_{Target} = \left(\frac{V_{rail} \times \% \_ripple}{I_{MAX \, dynamic}}\right) = \left(\frac{V_{ripple}}{I_{MAX \, dynamic}}\right)$$

© 2009 Altera Corporation—Public

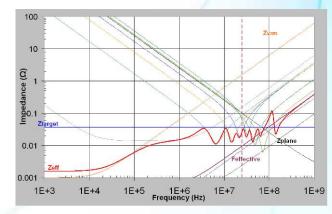

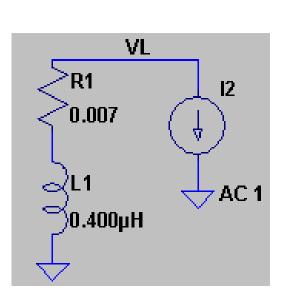

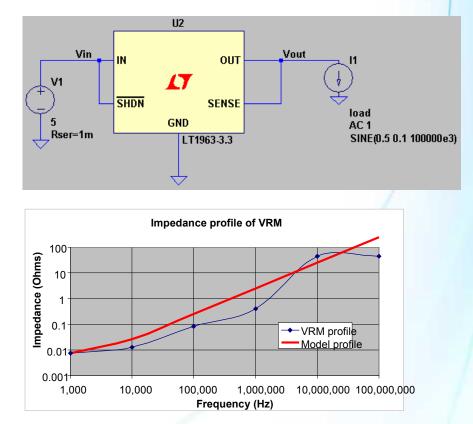

### **Selecting Voltage Regulator Module**

- The VRM has an impedance profile that behaves like an inductor and resistor in series

- Custom option in PDN tool to model any VRM

#### © 2009 Altera Corporation—**Public**

#### Package Choice – Stratix IV GX Device Package Plan

| Device                              | F780<br>(29 mm)           | F1152<br>(35 mm)           | F1152<br>(35 mm)           | F1517<br>(40 mm)           | F1760<br>(43 mm)           | F1932<br>(45 mm)           |

|-------------------------------------|---------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| EP4SGX70                            | 368, 28, 8                |                            | 480 <mark>, 56</mark> , 24 |                            | Pi                         | n                          |

| EP4SGX110                           | 36 <mark>8, 2</mark> 8, 8 | 368 <mark>, 28</mark> , 16 | 480 <mark>, 56</mark> , 24 |                            | mi                         | gration                    |

| EP4SGX180                           | 36 <mark>8, 2</mark> 8, 8 | 560 <mark>, 44</mark> , 16 | 560, 44, 24                | 73 <mark>6, 88</mark> , 36 |                            |                            |

| EP4SGX230<br>1 <sup>st</sup> device | 368, 28, 8                | 560 <mark>, 44</mark> , 16 | 560, 44, 24                | 736 <mark>, 88</mark> , 36 |                            |                            |

| EP4SGX290                           | 288, 0, 16                | 560 <mark>, 44</mark> , 16 | 560 <mark>, 44</mark> , 24 | 736 <mark>, 88</mark> , 36 | 864 <mark>, 88</mark> , 36 | 904 <mark>, 98</mark> , 48 |

| EP4SGX360                           | 28 <mark>8, 0</mark> , 16 | 560 <mark>, 44</mark> , 16 | 560 <mark>, 44</mark> , 24 | 736 <mark>, 88</mark> , 36 | 864 <mark>, 88</mark> , 36 | 904 <mark>, 98</mark> , 48 |

| EP4SGX530<br>2 <sup>nd</sup> device |                           |                            | 560, 44, 24                | 736, 88, 36                | 864, 88, 36                | 904, 98, 48                |

Total I/O, LVDS, transceiver counts

ounts

Notes:

Flip-chip ball-grid array (BGA) with 1.0-mm pitch Details subject to change

→ 14-layer package substrate with increased onpackage decoupling (OPD)

#### EP4SGX230HF35C4(N)

H, K, N all have enhanced OPD

© 2009 Altera Corporation—Public

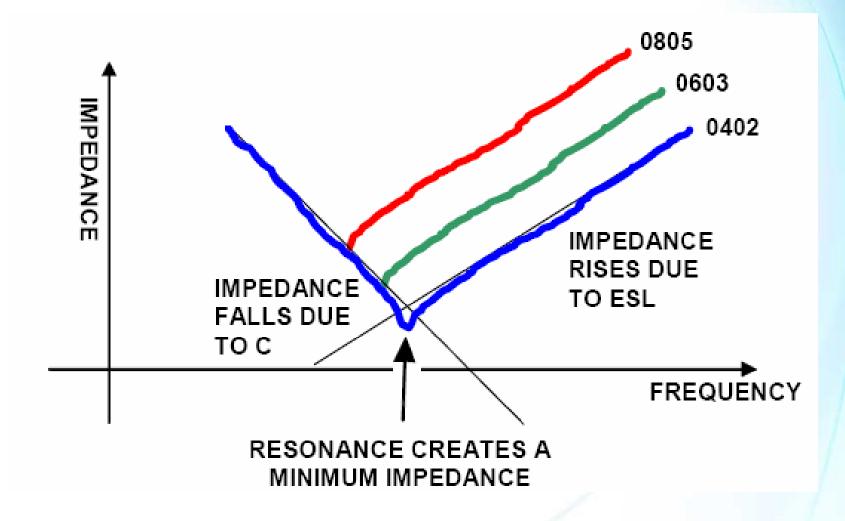

### **Package and Die Features**

|              | <b>f</b> <sub>effective</sub> <b>−</b> |                              |  |

|--------------|----------------------------------------|------------------------------|--|

| Supply       | EP4SGX230FF35<br>(8 layers)            | EP4SGX230HF35<br>(14 layers) |  |

| VCC          | ~25 MHz                                | ~24 MHz                      |  |

| VCCA_(L/R)   | 80 MHz                                 | ~20 MHz                      |  |

| VCCR_(L/R)   | ~50 MHz                                | ~20 MHz                      |  |

| VCCT_(L/R)   | ~50 MHz                                | ~20 MHz                      |  |

| VCCHIP_(L/R) | 80 MHz                                 | ~60 MHz                      |  |

Typical maximum frequency needed to be decoupled for different Stratix IV GX packages (This is device dependent. You need to use the PDN tool.)

Note: preliminary data

| Silicon and package features                                                                                                          | Benefits                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>8:1:1 – I/O:GND:PWR ratio</li> <li>On-die decoupling<br/>capacitors</li> <li>On-package decoupling<br/>capacitors</li> </ol> | <ol> <li>Reduces loop inductance         <ul> <li>→ reduces SSN</li> </ul> </li> <li>Improves power quality</li> <li>Improves power quality</li> </ol> |

© 2009 Altera Corporation—Public

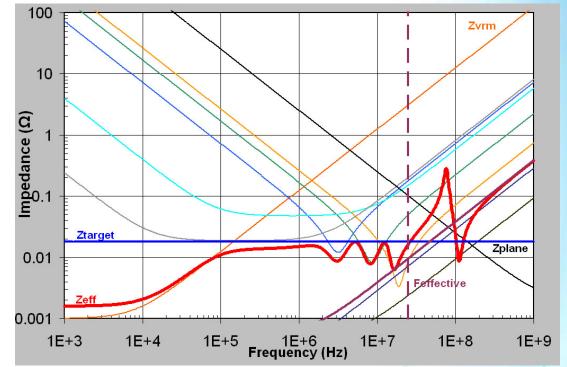

# Use f<sub>effective</sub> to Reduce Over-Design

- PCB decoupling capacitors are ineffective in reducing PDN |Z| beyond f<sub>effective</sub>

- PCB capacitors are limited due to system ESL

- Device OPD/ODC dominate at high frequencies

- f<sub>effective</sub> is device specific

- f<sub>effective</sub> calculation takes die, package, and PCB parasitics

Frequency

© 2009 Altera Corporation—Public

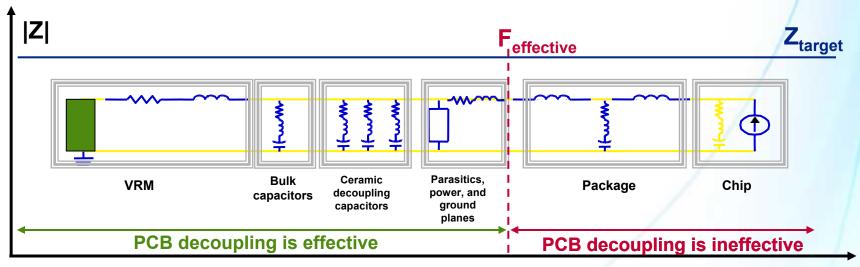

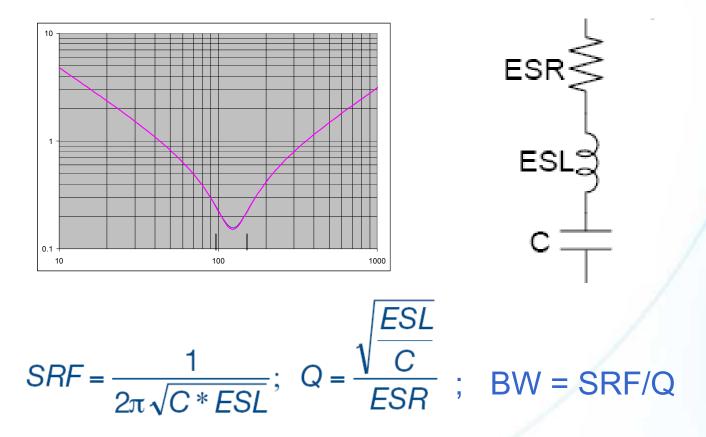

### **Properties of Decoupling Capacitor**

The most effective area of decoupling occurs within the bandwidth of any given capacitor

© 2009 Altera Corporation—Public

#### Z Profile vs. Package

© 2009 Altera Corporation—Public

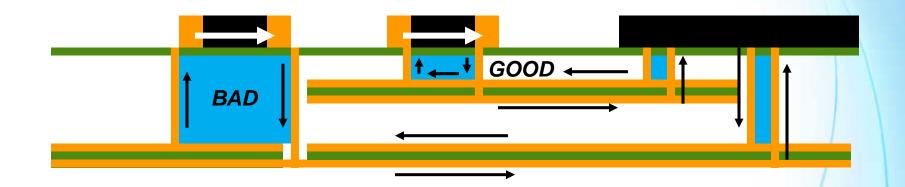

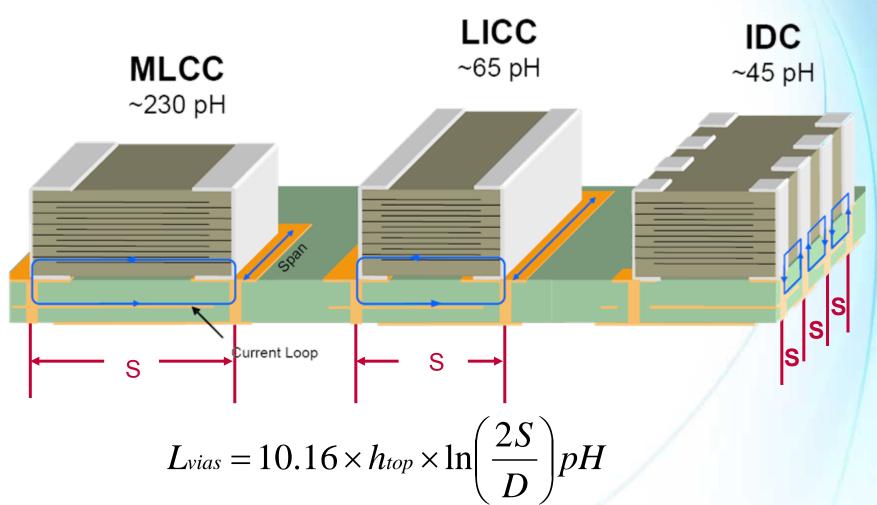

### **Mounting Inductance**

Reduce mounting inductance

- Place capacitor as close as possible to load

- Place capacitor on load side of board

- Place power plane for power delivery close to load

- Place power and GND planes adjacent for interplane capacitance

- Place vias to power and ground on capacitor as close as possible

© 2009 Altera Corporation—Public

#### **Loop Inductances and Capacitor Geometry**

#### **Courtesy of AVX**

© 2009 Altera Corporation—Public

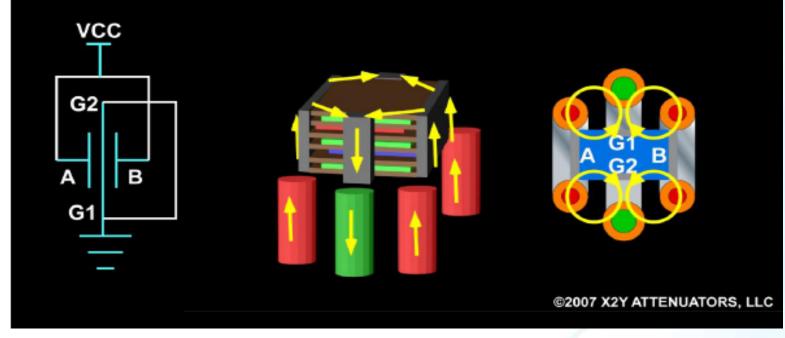

#### **Loop Inductance on X2Y Geometry**

#### X2Y<sup>®</sup> BYPASS APPLICATION FOUR SMALL INDUCTION LOOPS BETWEEN TERMINALS AND VIAS

#### **Courtesy of X2Y**

© 2009 Altera Corporation—Public

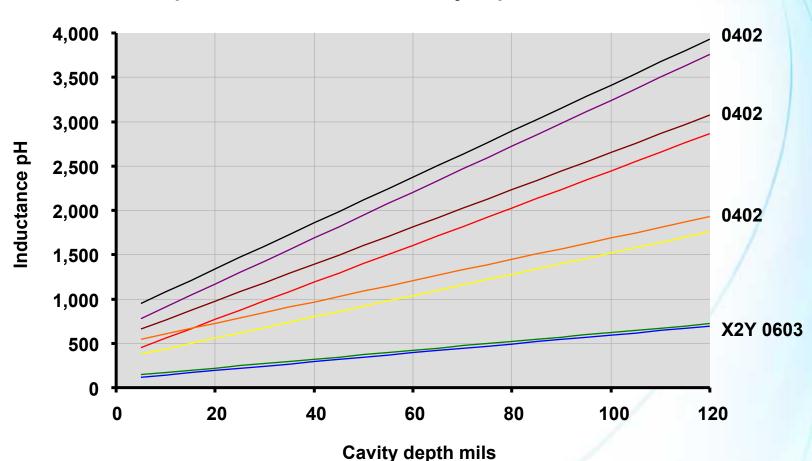

#### **Capacitor Geometry and Inductive Loops**

#### Capacitor inductance vs. cavity depth from surface

#### **Courtesy of X2Y**

#### © 2009 Altera Corporation—Public

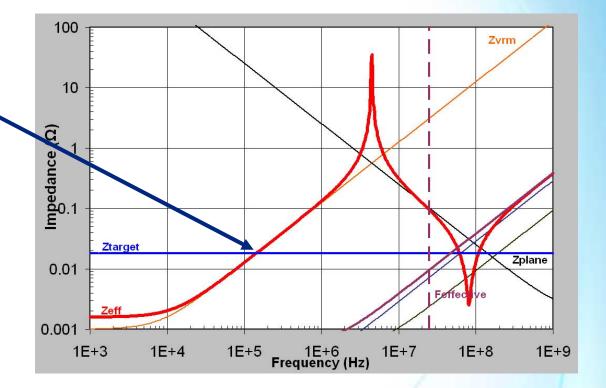

- Select VRM

- Start at the lowest frequency where Z<sub>eff</sub> crosses Z<sub>target</sub>

■ ~150 kHz

Add large capacitors until Z<sub>eff</sub> < Z<sub>target</sub> at target frequency

© 2009 Altera Corporation—Public

100 Added 4 x 220µF bulk Zvrm capacitors 10 New crossing point -Add smaller capacitors Impedance (9 Ztarget Zplane 0.01 | Feffec ve 0.001 1E+5 1E+3 1E+4 1E+7 1E+8 1E+9 1E+6 Frequency (Hz)

© 2009 Altera Corporation—Public

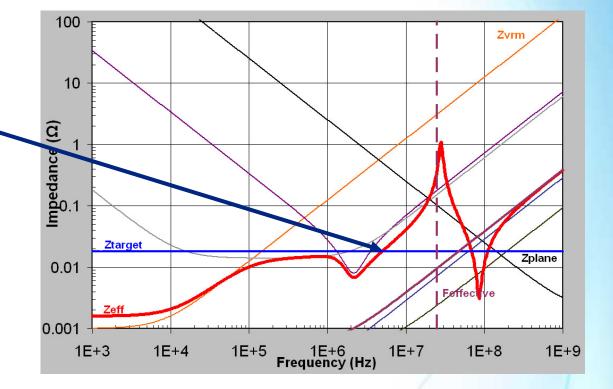

- 4 x 220µF bulk capacitors, 1 x 4.7µF MLCC capacitor

- New crossing point } ·

- Add smaller capacitors

- Until crossing point ≥ past f<sub>effective</sub>

© 2009 Altera Corporation—Public

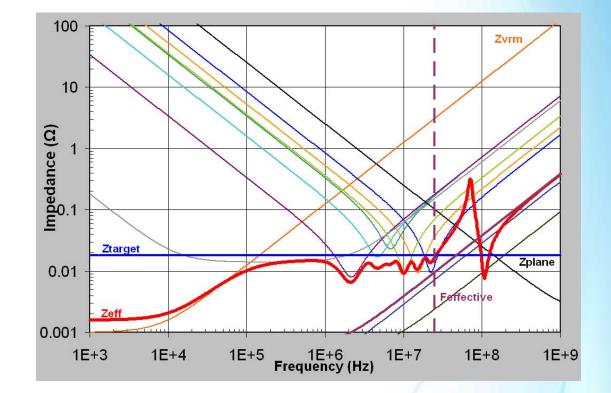

Final bypass capacitor selection

4 x 220µF bulk cap 1 x 4.7µF MLCC 0603 1 x 1µF MLCC 0603 1 x 0.47µF MLCC 0603 2 x 0.22µF MLCC 0402 3 x 100nF MLCC 0402 4 x 47nF MLCC 0402 **Total 15 caps**

© 2009 Altera Corporation—Public

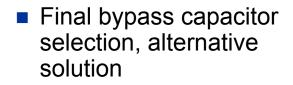

3 x 220µF bulk cap 4 x 10µF bulk cap 1 x 2.2µF MLCC 0603 1 x 0.47µF MLCC 0603 X2Y 3 x 100nF MLCC 0603 X2Y **Total 12 caps**

#### Many different solutions – still needs engineering skill for optimal solution

© 2009 Altera Corporation—Public

### Summary

- Innovative architecture and advanced process technologies ease PDN design

- Programmable Power Technology

- Stratix IV GX FPGAs lowest power, high-performance FPGAs

- Arria II GX FPGAs lowest power, cost-optimized FPGAs with up to 3.75-Gbps transceivers

- Best-in-class FPGA power modeling

- Early power estimator and Quartus II PowerPlay power analyzer

- Accurate power estimator

- Allows power optimization

- Ease of design with Altera's PDN tool

- Fairly accurate, easy-to-use spreadsheet tool

- Provides a scientific way (FDTIM) to decouple power rails in the system

- As accurate as the inputs provided by the user

- Has proved very useful while designing PDN for Altera boards

© 2009 Altera Corporation—Public

### **More Information**

- Board Design Resource Center

- PDN tool

- Channel design guidelines

- PCB and stack-up design considerations

- Memory interfacing, thermal considerations, and much more

- www.altera.com/board

- Power distribution network design tool

- Altera PDN Design Tool

- Altera PDN Design Tool User Guide

- Online training <u>Power Distribution Network Design for Stratix III and</u> <u>Stratix IV FPGAs</u>

- For more information on FDTIM (method behind PDN tool), refer to <u>Comparison of Power Distribution Network Design</u> <u>Methods (PDF)</u>

© 2009 Altera Corporation—Public

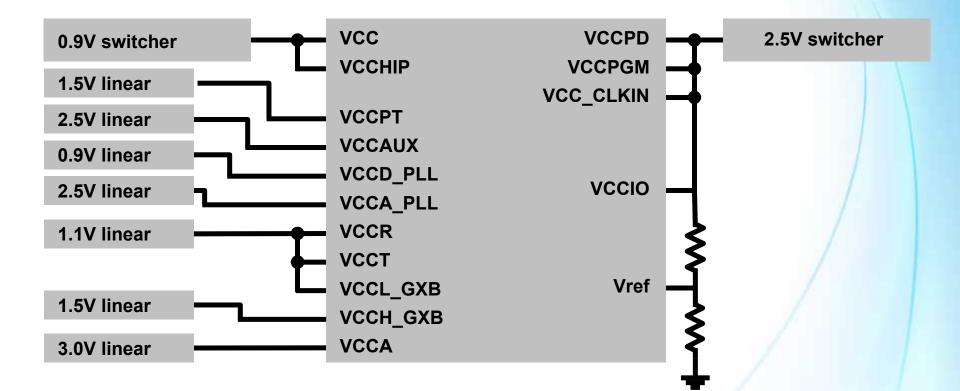

## **Stratix IV GX Power Rails**

#### VCCBAT not shown

© 2009 Altera Corporation—Public

### Stratix IV GX Power Rails (Min. Combined)

| No | Rail name   | Voltage   | Voltage<br>ripple<br>tolerance | Description                            |

|----|-------------|-----------|--------------------------------|----------------------------------------|

| 1  | VCC         | 0.9V      | <del>\$</del> 3.3%             | Core and periphery                     |

|    | VCCHIP      | 0.9V      | <del>+</del> 5%*               | *Transceiver PCI Express hard IP block |

| 2  | VCCPD       | 2.5V      | <del>\$</del> 5%               | I/O pre-drivers                        |

|    | VCCPGM      | 2.5V      | <del>\$</del> 5%               | Configuration I/Os                     |

|    | VCC_CLKIN   | 2.5V      | <del>\$</del> 5%               | VIO clock input pins                   |

| 3  | VCCPT       | 1.5V      | <del>+</del> 3.3%              | Programmable Power Technology          |

| 4  | VCCAUX      | 2.5V      | <del>\$</del> 5%               | Programmable Power Technology aux.     |

| 5  | VCCD_PLL    | 0.9V      | <del>+</del> 3.3%              | PLL digital                            |

| 6  | VCCA_PLL    | 2.5V      | <del>\$</del> 5%               | PLL analog                             |

| 7  | VCCR        | 1.1V      | <del>\$</del> 5%               | Transceiver analog receive             |

|    | VCCT        | 1.1V      | <del>\$</del> 5%               | Transceiver analog transmit            |

|    | VCCL_GXB    | 1.1V      | <del>\$</del> 5%               | Transceiver clock distribution         |

| 8  | VCCH_GXB    | 1.5V      | <del>\$</del> 5%               | Transceiver block buffers              |

| 9  | VCCA        | 3.0V      | <del>\$</del> 5%               | Transceiver analog Tx/Rx driver        |

| 10 | VCCIO[23:0] | 1.2V-3.0V | <del>\$</del> 5%               | 24 I/O banks                           |

#### \* If connected to VCC – supply must support tighter VCC tolerance (3.3%)

© 2009 Altera Corporation—Public

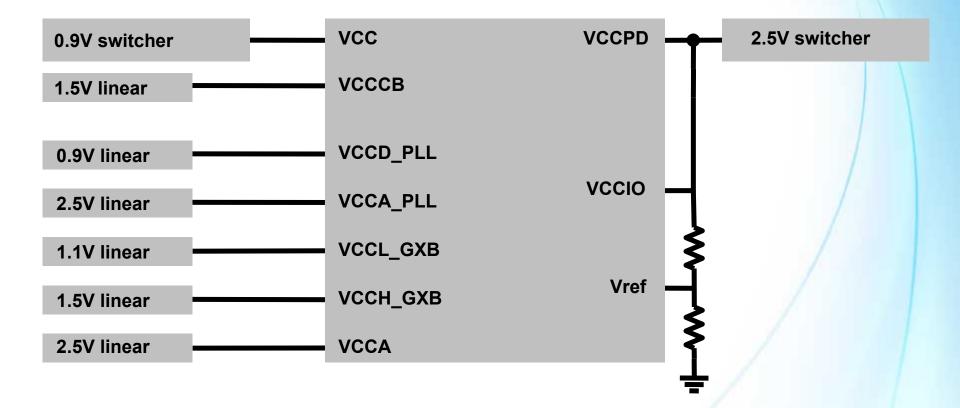

#### **Arria II GX Power Rails**

#### VCCBAT not shown

© 2009 Altera Corporation—Public

# Arria II GX Power Rails (Min. Combined)

| No | Rail name   | Voltage   | Voltage<br>ripple<br>tolerance | Description                                        |

|----|-------------|-----------|--------------------------------|----------------------------------------------------|

| 1  | VCC         | 0.9V      | <del>\$</del> 3.3%             | Core, periphery, PCIe hard IP, and transceiver PCS |

| 2  | VCCPD       | 2.5V      | <del>\$</del> 5%               | I/O pre-drivers                                    |

| 3  | VCCCB       | 1.5V      | <del>\$</del> 5%               | Configuration RAM supply                           |

| 4  | VCCD_PLL    | 0.9V      | <del>\$</del> 3.3%             | PLL digital supply                                 |

| 5  | VCCA_PLL    | 2.5V      | <del>\$</del> 5%               | PLL analog supply                                  |

| 6  | VCCL_GXB    | 1.1V      | <del>\$</del> 5%               | Transceiver PMA Tx/Rx and clock supply             |

| 7  | VCCH_GXB    | 1.5V      | <del>\$</del> 5%               | Transceiver PMA Tx buffer supply                   |

| 8  | VCCA        | 2.5V      | <del>\$</del> 5%               | Transceiver PMA regulator supply                   |

| 9  | VCCIO[23:0] | 1.2V-3.0V | <del>\$</del> 5%               | 24 I/O banks                                       |

© 2009 Altera Corporation—Public