|

ALTERAРЧ Mega Function WizardДТ ИХАГКЏМіШЕЧОю РжАэ ДыЛѓ Programmable Device БИСЖРЧ ШПРВРћРЮ ЛчПыРЛ РЇЧЯПЉ УжРћШ Йз ЛчРќ АЫСѕЕШ IP КэЗЯРЛ НБАд Л§МКНУФбСжДТ ЕЕБИРдДЯДй... Mega Function WizardИІ ЛчПыЧЯИщ МГАшРкДТ РЯЙнРћРЮ БтДЩРЛ ЖЧ МГАшЧв ЧЪПф ОјРЬ Дѕ ИЙРК НУАЃАњ ГыЗТРЛ НУНКХл ЗЙКЇРЧ СІЧАРЛ АГМБЧЯАэ ТїКАШЧЯДТЕЅ РќГфЧв Мі РжНРДЯДй... ЖЧЧб Mega Function WizardДТ БтСИ HDL (Hardware Description Language) МГАшИІ ЦїЧдЧб И№Еч PLD (Programmable Logic Device) МГАш ЙцНФРЛ СіПјЧеДЯДй... КЙРтЧб НУНКХл БИСЖИІ БИЧіЧв АцПьПЁ РЬЙЬ ИИЕщОюСЎ РжДТ IPИІ ЛчПыЧдРИЗЮНс МГАш НУАЃРЛ ДмУрЧв Мі РжНРДЯДй... ALTERAРЧ Mega Function WizardДТ ИХАГКЏМіШЕЧОю РжАэ ДыЛѓ Programmable Device БИСЖРЧ ШПРВРћРЮ ЛчПыРЛ РЇЧЯПЉ УжРћШ Йз ЛчРќ АЫСѕЕШ IP КэЗЯРЛ НБАд Л§МКНУФбСжДТ ЕЕБИРдДЯДй... Mega Function WizardИІ ЛчПыЧЯИщ МГАшРкДТ РЯЙнРћРЮ БтДЩРЛ ЖЧ МГАшЧв ЧЪПф ОјРЬ Дѕ ИЙРК НУАЃАњ ГыЗТРЛ НУНКХл ЗЙКЇРЧ СІЧАРЛ АГМБЧЯАэ ТїКАШЧЯДТЕЅ РќГфЧв Мі РжНРДЯДй... ЖЧЧб Mega Function WizardДТ БтСИ HDL (Hardware Description Language) МГАшИІ ЦїЧдЧб И№Еч PLD (Programmable Logic Device) МГАш ЙцНФРЛ СіПјЧеДЯДй... КЙРтЧб НУНКХл БИСЖИІ БИЧіЧв АцПьПЁ РЬЙЬ ИИЕщОюСЎ РжДТ IPИІ ЛчПыЧдРИЗЮНс МГАш НУАЃРЛ ДмУрЧв Мі РжНРДЯДй...

РЬЗЏЧб Mega Function WizardПЁМ СІАјЕЧДТ ИоИ№ИЎАќЗУ IPРЧ СОЗљДТ LPM_RAM_DP, LPM_RAM_IO, LPM_RAM_DQ РЬЗИАд 3СОРдДЯДй... БзСп LPM_RAM_DQДТ Single Port MemoryИІ РЧЙЬЧЯИч, ПЉБтМДТ ЙйЗЮ РЬLPM_RAM_DQРЧ ЕПРлЙцЙ§ПЁ ДыЧи АЃЗЋШї МГИэРЛ ЧеДЯДй... (2000.5.15) РЬЗЏЧб Mega Function WizardПЁМ СІАјЕЧДТ ИоИ№ИЎАќЗУ IPРЧ СОЗљДТ LPM_RAM_DP, LPM_RAM_IO, LPM_RAM_DQ РЬЗИАд 3СОРдДЯДй... БзСп LPM_RAM_DQДТ Single Port MemoryИІ РЧЙЬЧЯИч, ПЉБтМДТ ЙйЗЮ РЬLPM_RAM_DQРЧ ЕПРлЙцЙ§ПЁ ДыЧи АЃЗЋШї МГИэРЛ ЧеДЯДй... (2000.5.15)

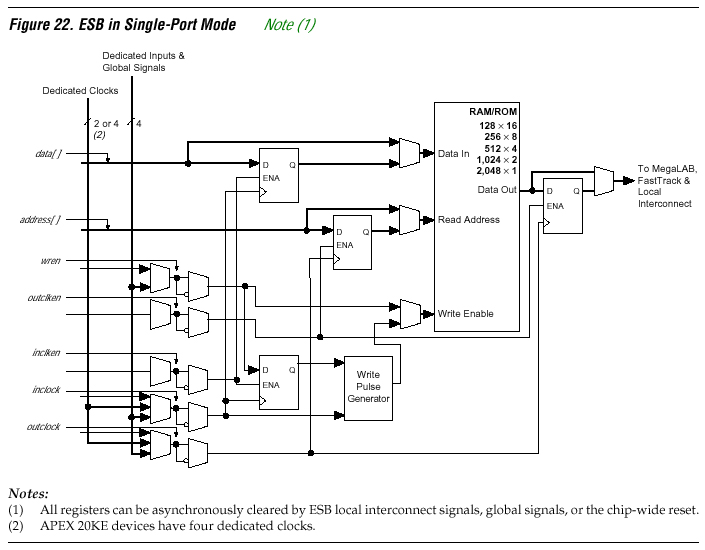

ОЦЗЁ БзИВРК APEX 20K DeviceПЁМ СІАјЧЯДТ LPM_RAM_DQРЧ БИСЖРдДЯДй... ОЦЗЁ БзИВРК APEX 20K DeviceПЁМ СІАјЧЯДТ LPM_RAM_DQРЧ БИСЖРдДЯДй...

БзИВПЁМ КИРЬДТ АЭУГЗГ 2KbitРЧ MemoryСжКЏПЁ ЙшФЁЕШ Flip FlopРЧ ШАПы ЙцЙ§ПЁ ЕћЖѓ МјМі КёЕПБтНФ Memory ШЄРК ЕПБтНФ MemoryЗЮМ ШАПыРЬ АЁДЩЧеДЯДй... БзИВПЁМ КИРЬДТ АЭУГЗГ 2KbitРЧ MemoryСжКЏПЁ ЙшФЁЕШ Flip FlopРЧ ШАПы ЙцЙ§ПЁ ЕћЖѓ МјМі КёЕПБтНФ Memory ШЄРК ЕПБтНФ MemoryЗЮМ ШАПыРЬ АЁДЩЧеДЯДй...

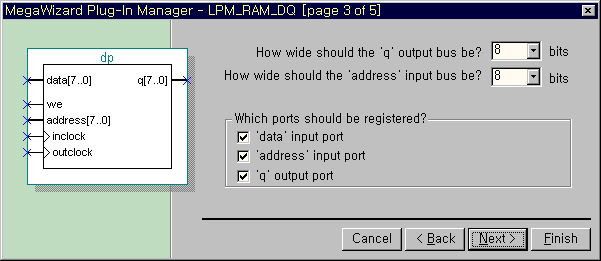

ОЦЗЁРЧ БзИВРК MAX+plus II ШЄРК Quartus S/WРЧ MegaWizard Plug-In ManagerПЁМ LPM_RAM_DQ ModuleРЛ МБХУЧЯПДРЛ ЖЇ ГЊПРДТ РдУтЗТ ЦЏМКРЛ СЄРЧЧЯДТ МБХУЧзИё ШИщРдДЯДй... "Address"РЧ WidthПЭ Data OutputРЮ "Q"РЧ DepthИІ СЄРЧЧЯДТ ЧзИёАњ, АЂАЂРЧ РдУтЗТПЁ ДыЧи ClockАњРЧ ЕПБтИТУуРЛ МБХУЧв Мі РжДТ "Which ports should be registered?"ЖѓДТ МБХУЧзИёРЬ РжНРДЯДй... "Which ports should be registered?" КЮКаПЁМ МБХУЕШ ЧзИёЕщРК ЧиДчPinРИЗЮ DataАЁ ЕщОюПРАХГЊ ГЊАЅ ЖЇ ЧзЛѓ ClockПЁ ЕПБтАЁ ЕЧОю ПђСїРдДЯДй... ОЦЗЁ БзИВПЁМДТ И№ЕЮ МБХУРЬ ЕЧОюРжДТ ЛѓХТИІ ГЊХИГРДЯДй... БтКЛРћРИЗЮДТ 'q' output portДТ МБХУРЬ ЕЧОюРжСі ОЪНРДЯДй... ОЦЗЁРЧ БзИВРК MAX+plus II ШЄРК Quartus S/WРЧ MegaWizard Plug-In ManagerПЁМ LPM_RAM_DQ ModuleРЛ МБХУЧЯПДРЛ ЖЇ ГЊПРДТ РдУтЗТ ЦЏМКРЛ СЄРЧЧЯДТ МБХУЧзИё ШИщРдДЯДй... "Address"РЧ WidthПЭ Data OutputРЮ "Q"РЧ DepthИІ СЄРЧЧЯДТ ЧзИёАњ, АЂАЂРЧ РдУтЗТПЁ ДыЧи ClockАњРЧ ЕПБтИТУуРЛ МБХУЧв Мі РжДТ "Which ports should be registered?"ЖѓДТ МБХУЧзИёРЬ РжНРДЯДй... "Which ports should be registered?" КЮКаПЁМ МБХУЕШ ЧзИёЕщРК ЧиДчPinРИЗЮ DataАЁ ЕщОюПРАХГЊ ГЊАЅ ЖЇ ЧзЛѓ ClockПЁ ЕПБтАЁ ЕЧОю ПђСїРдДЯДй... ОЦЗЁ БзИВПЁМДТ И№ЕЮ МБХУРЬ ЕЧОюРжДТ ЛѓХТИІ ГЊХИГРДЯДй... БтКЛРћРИЗЮДТ 'q' output portДТ МБХУРЬ ЕЧОюРжСі ОЪНРДЯДй...

РЇРЧ МБХУ ЛчЧзРИЗЮ LPM_RAM_DQИІ Л§МКЧЯИщ ДйРНАњ ААРК ЕПРлРЛ ЧеДЯДй... РЇРЧ МБХУ ЛчЧзРИЗЮ LPM_RAM_DQИІ Л§МКЧЯИщ ДйРНАњ ААРК ЕПРлРЛ ЧеДЯДй...

- "we"АЁ HighРЯ АцПь Write, LowРЯ АцПь Read...

- 'data'ПЭ 'address[7..0]'ДТ "inclock"ПЁ ЕПБтАЁ ИТУпОю ЕПРл...

- 'q[7..0]'ИИРЬ "outclock"ПЁ ЕПБтАЁ ИТУпОю ЕПРл...

- "Wirte"ЕПРл ЛгИИОЦДЯЖѓ "Read"ЕПРлЕЕ "inclock"Ањ ПЌАшЕЧОю ПђСїРг...

- "outclock"РК ДмСі 'q[7..0]'РЧ УтЗТПЁИИ ПЌАќ... ("we"АЁ LowРЯ ЖЇ, "inclock"ПЁ ИТУпОю 'address[7..0]'ПЁ АЊРЬ СжОюСіИщ, ЧиДч ЙјСіРЧ dataАЁ 'q[7..0]' УтЗТ ЗЙСіНКХЭ ОеДмБюСі УтЗТРЬ ЕЧАэ, "outclock"ПЁ ИТУпОю НЧСІ 'q[7..0]'РИЗЮ dataАЁ УтЗТЕЪ...)

ОЦЗЁРЧ ЦФЧќРК РЇПЁМ МГИэЧб ГЛПыРЧ РЬЧиИІ ЕНАэРк "inclock"Ањ "outclock"РЛ ПЉЗЏ СЖАЧРИЗЮ ЙйВуКИИщМ Quartus S/WПЁМ Function SimulationЧб АсАњРдДЯДй... ОЦЗЁРЧ ЦФЧќРК РЇПЁМ МГИэЧб ГЛПыРЧ РЬЧиИІ ЕНАэРк "inclock"Ањ "outclock"РЛ ПЉЗЏ СЖАЧРИЗЮ ЙйВуКИИщМ Quartus S/WПЁМ Function SimulationЧб АсАњРдДЯДй...

ПЉБтБюСіАЁ LPM_RAM_DQ ЕПРлПЁ ДыЧб АЃЗЋЧб МГИэРдДЯДй... Block DiagramАњ Function SimulationАсАњИІ КёБГЧиМ КИНУИщ ЕЕПђРЬ ЕЧНУИЎЖѓ Л§АЂЕЫДЯДй... ПЉБтБюСіАЁ LPM_RAM_DQ ЕПРлПЁ ДыЧб АЃЗЋЧб МГИэРдДЯДй... Block DiagramАњ Function SimulationАсАњИІ КёБГЧиМ КИНУИщ ЕЕПђРЬ ЕЧНУИЎЖѓ Л§АЂЕЫДЯДй...

|

![]()