# Simple Pipelined System

- All Spice problems in this homework are to be done for technologies

- tsmc018.model, Vdd = 2.5 V, default temp

- $-\,$  all input waveforms should have rise/fall times of 200 ps.

- It is encouraged that you work in teams of two (if you work alone, you must provide me with a reason).

- · Will be worth twice that of previous assignments.

BR 6/00

### Goal

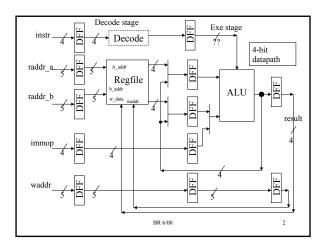

- Implement a simple pipelined system using static CMOS

- · Goal is performance

- · Problems you will face

- Clock network will have a significant load

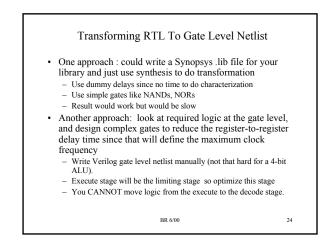

- Must generate a gate level netlist from an RTL description

- Must choose your own cells for this for this implementation.

BR 6/00

3

# Design Constraints

- Create your own Verilog, Spice level gate library for this design

- Any complex gate design is valid

- For spice level netlists, use the P\_def and N\_def transistor subcells used in previous labs

- Other than inverters, no transistor can exceed a width of 8\*wmin.

For inverters, cannot use anything transistor larger than 32\*wmin.

- No layout just spice level netlists

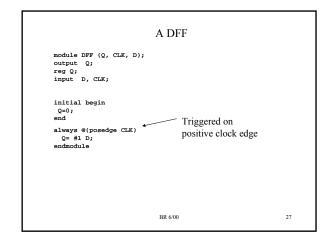

- Can use any DFF design that you can find

- Might want to consider integrating logic with latches to increase speed

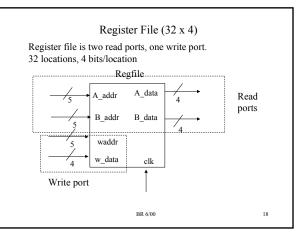

- The register file will be simulated using a Verilog-A model in the spice level netlist.

BR 6/00

# Design Constraints (cont.)

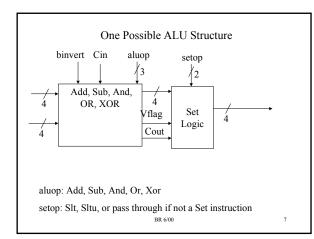

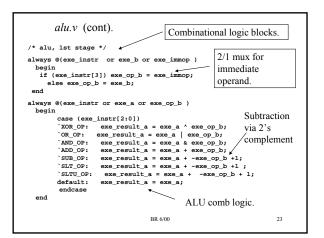

- You are free to design the ALU anyway you want to meet the required functionality

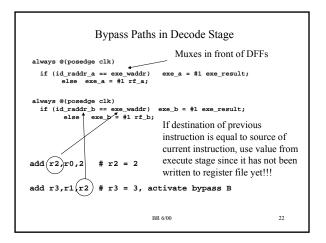

- You cannot move any logic from the EXE stage back into the Decode stage other than doing pre-decoding on the instruction

- You must provide a Verilog gate level netlist that implements the RTL

- Must be compatible with the current Verilog testbench

- · I will provide a Spectre testbench at a later date

- All inputs, including the clock, will driven by 1X buffers

- All extra drive will have to provided by your spice netlist implementation

BR 6/00

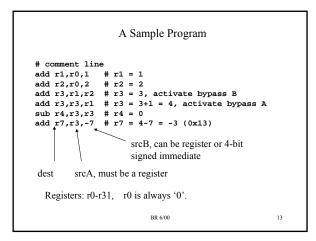

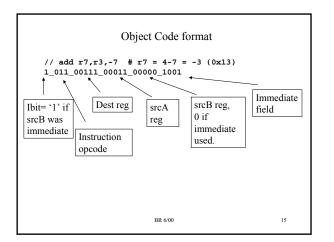

# Supported Instructions

- · Three operand format

- op rdest, ra, rb

rdest = ra op rb

- · Arithmetic: add, sub

- · Logic: xor, and, or

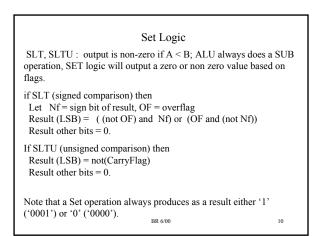

- · Other: slt, sltu

- Set-Less-Than (slt rdest, ra, rb)

Rdest = 1 if ra < rb (signed comparison)</li>

- Set-Less-Than-Unsigned (sltu rdest, ra,rb)

Rdest = 1 if ra < rb (unsigned comparison)</li>

BR 6/00

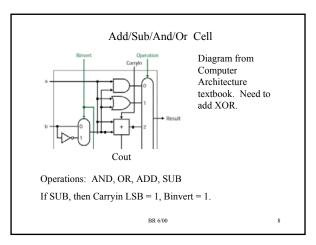

Overflow Flag Logic Overflow logic depends on whether doing an addition or subtraction: if (addition) overflow = (Amsb and Bmsb and (not Smsb )) or ( ( not Amsb) and (not Bmsb) and Smsb) i.e. For addition, if sign bits of operands are the same, but the result sign bit is different, then OVERFLOW has occurred. Smsb is the most significant bit of the result. If (subtraction) OF = (Amsb and (not Bmsb) and (not Smsb) ) or ((not Amsb) and Bmsb and Smsb) Note: In all cases, Binvert = 1 for subtraction, Binvert = 0 for add

BR 6/00

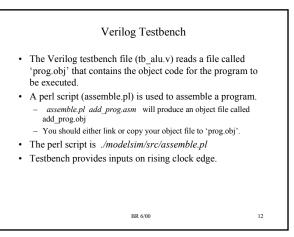

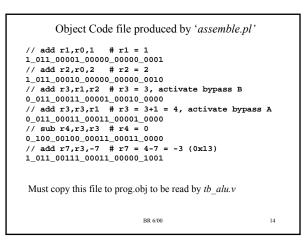

# Verilog RTL, Testbench

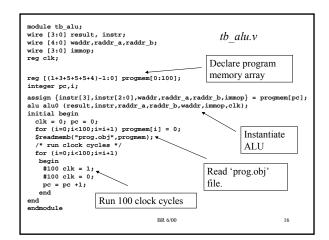

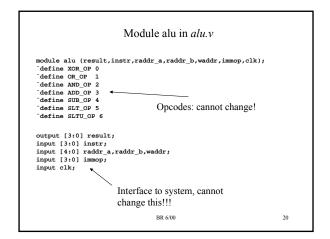

- In distribution, the directory ./modelsim/src/alu\_rtl contains the verilog files

- alu.v RTL for pipelined system

- tb\_alu.v testbench for alu.v

- · To place modelsim on path do 'swsetup modelsim'

- To compile files do

- cd ./modelsim/src/alu\_rtl

- gmake –f alu\_rtl/Makefile

- · To run simulation:

- qhsim –lib alu\_rtl tb\_alu –c –do "run 20 us;quit"

```

BR 6/00

```

11

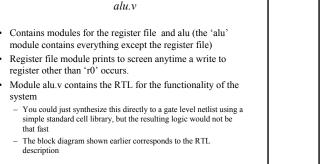

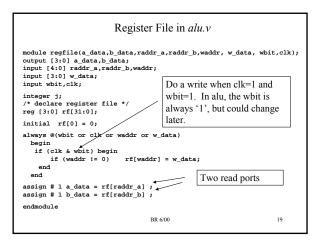

- · Contains modules for the register file and alu (the 'alu'

BR 6/00

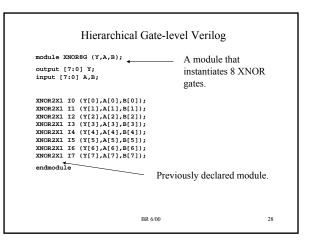

# Writing Gate-level Verilog Modules

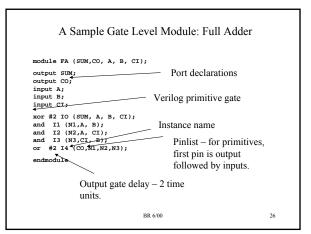

- The file /sample\_files/libcells.v has some sample module definitions for common library functions like nands, nors, xors, etc.

- When writing your gate level modules, do the following: - Use either UPPER case or LOWER case for all terminal/module names

- Do NOT use mixed case

- I would suggest using lowercase for everything (more readable).

- Verilog is case sensitive

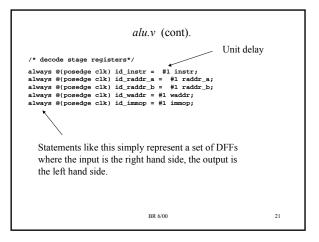

- Use unit delays for gate level modules

BR 6/00

25

# Due Dates Completed Spice Simulation are due on October 3<sup>rd</sup> (two weeks from today). Verilog Gate level simulation due on Thursday Sept 26<sup>th</sup> (this does not have to be the final gate level netlist, just a progress check). Expect two files: libcells.v that has gate level modules and alu.v that is gate level netlist and register file module (do not change the register file module)

Rankings

- I will rank designs by achievable clock frequency

Spectre testbench will be provided by Thursday, Sept 26<sup>th</sup>.

- Upper 1/3 of class will get 25 points added to any test grade.

- Middle 1/3 will get 12 pts added to any test grade.

- Bottom 1/3 will get no extra points.