## Details

- If the last digit of your student ID modulo 4 is:

- 0, use 1.4/1 for your 1X inverter, 0.18 TSMC technology

- 1, use 2/1 for your 1X inverter, 0.18 TSMC technology

- 2, use 1.4/1 for your 1X inverter, 0.35 TSMC technology

- 3, use 2/1 for your 1X inverter, 0.35 TSMC technology

- Scale your 2-input NAND based upon your 1X inverter

- Use appropriate GEO parameters in your NAND model

- When optimizing the delay, optimize only for TPHL

- will assume that TPLH will be ok

- this should reduce the simulation workload

- Assume that you only have gate sizes of 1x to 6x available in 0.5x steps.

BR 6/00

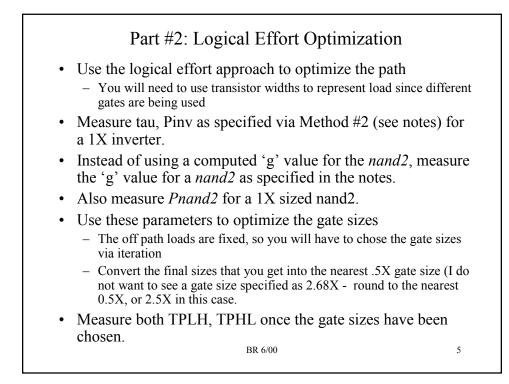

Part #1: Tilos Optimization

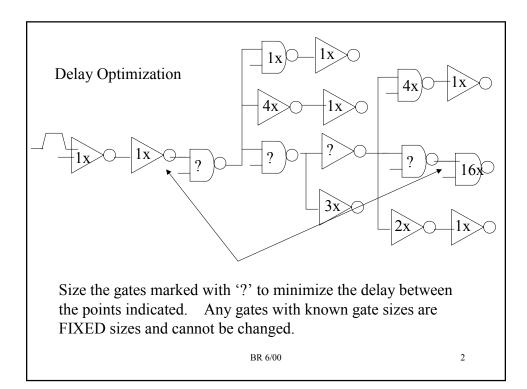

Use the Tilos algorithm to optimize the gate sizes in 0.5X steps.

Increase gate sizes by 0.5X during simulation

All the gates marked with '?' are available for sizing.

Once the final gate sizes have been chosen, record both TPLH and TPHL through the optimized path.

4

3