## Fall '01 Project

- The Fall '00 project had each team design a small standard cell library for AMI 0.5u technology

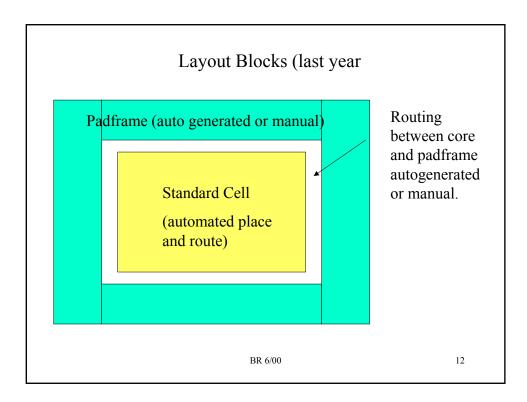

- Cadence tools to place/route the design

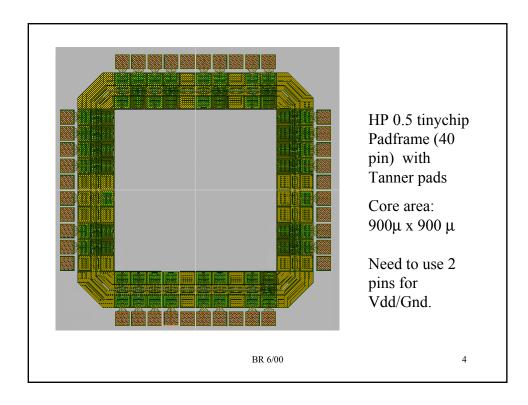

- A MOSIS tinychip padframe (40 pin) was used for the IO

- W. Tan (a student from that class) took the best library from that effort, cleaned it up, and have since used it to fabricate a non-trivial design

- This library will be made available to you for this semester's project

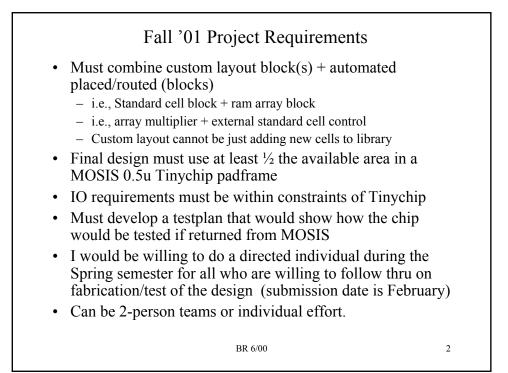

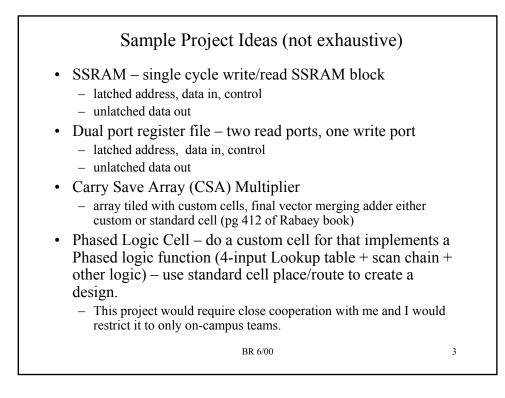

- For Fall '01, you must do a design that combines custom layout + automated cell-based layout to create an 'interesting' VLSI system

BR 6/00

1

## Test Plan

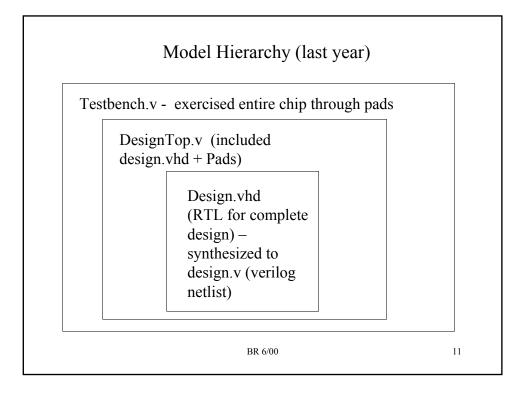

• You will probably need to surround your design with some sort of 'testbench' that will feed inputs to the design and capture outputs within the limits of the Tinychip padframe

- Tinychip has 40 pins 38 IO's, need 2 pins for Vdd/Gnd

- testbench will have to multiplex design IO to limits of tinychip padframe

- E.G., assume your design is a  $16 \times 16 = 32$  multiplier that accomplishes 1 multiply per clock cycle.

- pinout could be Vdd, Gnd, Clk, Reset, Dir, D[31:0] (37 total pins)

- When DIR = 1, then D[31:0] are inputs and latch two 16-bit operands on rising clock edge.

- When DIR = 0, then D[31:0] are outputs and contain the 32-bit product

BR 6/00

5

| Tool Usage                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>The standard cell library in Cadence format will be provided<br/>along with tutorials for producing placed/routed standard cell<br/>block         <ul> <li>Verilog netlist used to specify the design</li> </ul> </li> </ul>                |

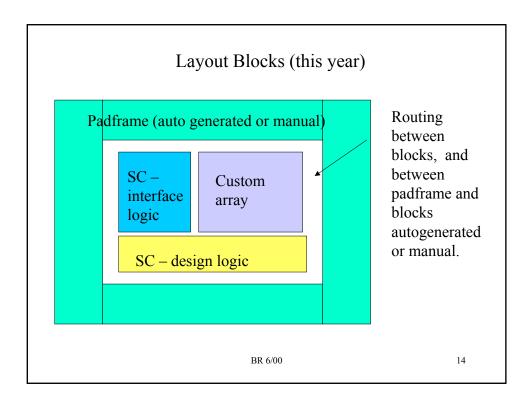

| <ul> <li>For custom layout, you will need to use Cadence</li> <li>You will probably be creating one more custom cells for your design</li> <li>'Tiling' of the cells into an array can either be done manually or automated via SKIL code</li> </ul> |

| <ul> <li>Routing between the standard cell block(s) and custom<br/>block(s) can either be automated or done manually</li> </ul>                                                                                                                      |

| • Routing between the padframe and the final design can either be automated or done manually                                                                                                                                                         |

| • You must make an attempt to do full chip transistor level simulation via IRSIM as final verification (more on this later).                                                                                                                         |

| BR 6/00 6                                                                                                                                                                                                                                            |

## Extra Points

- Extra points will be awarded if you use additional ECAD tool automation to produce your design above the minimum

- SKIL code used to automate 'tiling' of array cells

- Automated routing between standard cell block(s) and custom block(s)

- Automated routing between core and padframe

- I will give you tutorials/methodology for standard cell place/route

- To do the above 'extra' automation, you will have to read the Cadence documentation on your own and do experimentation.

- Project counts as 3<sup>rd</sup> test.

BR 6/00

7

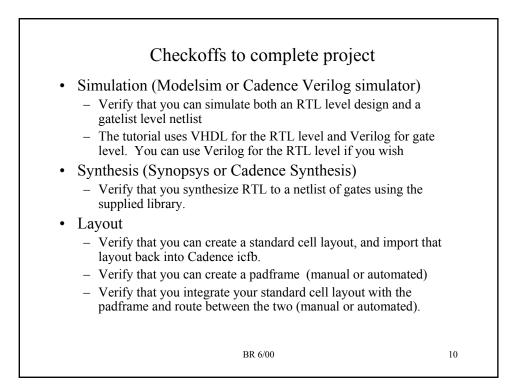

Simulations You must provide a gate level Verilog simulation of your COMPLETE chip (testbench + design) - Will provide Verilog models of standard cells - You will have to write Verilog models of any custom cells that you design (I can help in this, it is not hard). - This simulation is for functional verification only, not timing verification Once the layout is complete, you must provide a chip-level through-pad transistor-level simulation via IRSIM - IRSIM is switch-level simulator that works from an extracted transistor level netlist of the layout - Useful for finding fatal bugs like missing routes - Will talk about this later, you should practice IRSIM simulation on your custom cells first. Project is due at midnight on Sunday, December 2<sup>nd</sup>. BR 6/00 8