| System Timing with FFs                                                                                                                                                                                                                                  |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

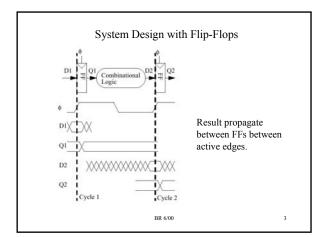

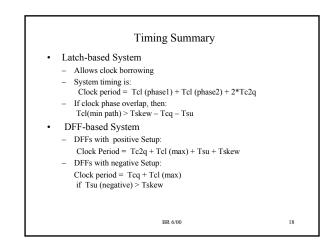

| Clock Period = $Tc2q + Tcl + Tsu + Tskew$                                                                                                                                                                                                               |   |

| Tc2q: Clock to Q prop delayTcl: max delay of combinational logicTsu: setup time of clockTskew : max clock skew                                                                                                                                          |   |

| Clock skew is the difference in clock edge arrival times at<br>different FFs in the system. If Clock arrives Tskew early,<br>then Tskew adds to Tsu. If clock arrives Tskew late, then<br>Tskew adds to Tc2q. Either way, additional delay is<br>Tskew. |   |

| BR 6/00                                                                                                                                                                                                                                                 | 5 |

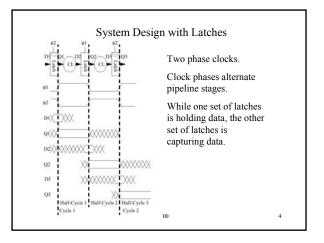

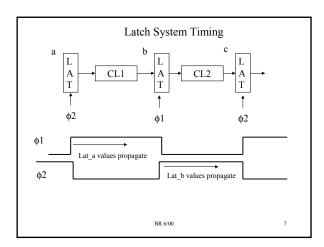

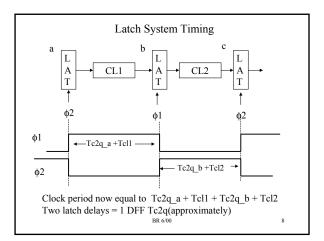

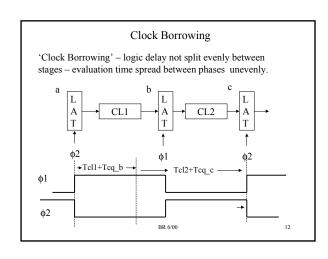

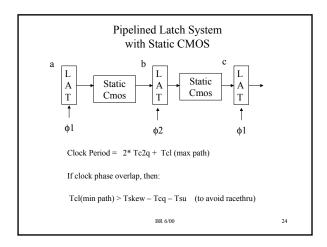

## System Timing with Latches At first glance, timing looks like (assume logic of FF example was broken evenly between two stages so total logic delay is same as FF example) Clock Period = C2Q (first latch) + Tlogic + Tsu + Tskew + C2Q (middle latch) + Tsu + Tskew However, actual equation is: Clock Period = C2Q (first latch) + Tlogic + C2Q (middle latch)

Tsu, Tskew does not enter into this equation because arrival of inputs from one phase can be used immediately.  $$_{\rm BR\,600}$$

## 5

## Self-Resetting CMOS (SRCMOS)

- SRCMOS differs from Domino logic in that the reset signal is generated locally

Less clock load

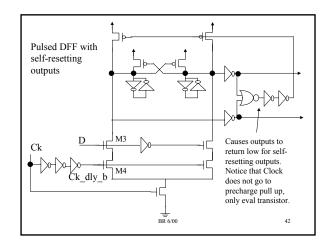

- Outputs are pulsed  $0{\rightarrow}1{\rightarrow}0,\,$  inputs assumed pulsed as well

- Because inputs are '0' at start of evaluation, then no need for evaluation transistor!

- No evaluation transistor means one less transistor in pulldown path means a faster circuit

- Many schemes for generating reset

- Delayed version of the clock

- Generate reset based on dual rail outputs

- Generate reset for an entire block of gates at one time

- Will look at this in more detail for decode circuits for RAMs.

BR 6/00

43