# Spectre Tutorial

- · Spectre will be used for transistor level simulation

- · To place on path,do: 'swsetup cadence-ncsu'

- Use online help or PDF docs at ~reese/cadence docs

- Documentation

- Spectre User Manual most helpful for first time users

- Spectre Reference Manual details on all available statements

- Verilog-A Reference Manual details on Verilog-A language

- Spectre HDL details Spectre HDL, a proprietary HDL. Has been largely replaced by standard languages such as Verilog-A.

However, Analog library model detailed in Verilog-A reference manual is written in Spectre HDL

BR 8/02

### More Docs

- Appendix D of Verilog-A reference gives a pre-defined library of Analog Component library

- Source code for these models are at: /opt/ecad/cadence/v4.45/ic\_4.45qsr2/tools/dfII/samples/artist/ahdlLib/

For model details, look at source code for a model under: model\_name/ahdl/ahdl.def

(e.g., delta\_probe/ahdl/ahdl.def)

Note: These models are written in Spectre HDL.

BR 8/02

# Spectre

- Spectre accepts either SPICE or Spectre syntax

- Spectre syntax less restrictive than SPICE (I.e., in Spectre syntax, element names do not have to start with a particular letter)

- In my files, will mix SPICE and Spectre syntax freely just because I am used to SPICE

- · The 'awd' program is used to view waveforms

- A powerful waveform viewer, but can take many button clicks to produce a value from a waveform. It is better to use HDL models for signal measurement purposes.

- Verilog-A is an extension of Verilog that supports analog concepts such as Voltage, Current

- Verilog-A can be called like sub-circuits from Spectre files

- I will use Verilog-A for things like measurements because it is easier, faster than popping up a waveform viewer. Will use waveform viewer for debugging.

- Predefined models in Affirma Analog Library are written in SpectreHDL

BR 8/02

# Example: Power, Delay Measurement Pmtr Pmtr Driver Load

Measure average power through DUT

Measure TPLH, TPHL of DUT.

ends P def

Grab zip archive 'spectre\_example.zip' from WWW page

BR 8/02

# Spectre Example Files

- · BSIM3V3 Model files from http://mosis.com

- ami06.m for AMI 0.6u process

- tsmc025.m for TSMC 0.25 process

- tsmc018.m for TSMC 0.18 process

- Transistor model names are 'N', 'P'.

- · Parameters lmin, wmin have been added to files:

- Lmin minimum channel length

- Wmin minimum gate width

- Specify L,W parameters for transistors in terms of these parameters and your designs can be tested with different processes.

BR 8/02 5

### Spectre Example Files (cont)

- 'def.m' defines 'N\_def', 'P\_def' models which calculate default values for AS, AD, PS, PD based upon L, W parameters

- Handy if just testing pre-layout designs (extracted transistors will always have these values).

- Default values for AS,AD, PS, PD in BSIM3V3 model is zero this is bad – always use non-zero geometry values.

```

subckt N_def (d g s b)

parameters L=lmin W=wmin

M0 (d g s b) N w=W l=L as=(W*1.5e-6) ad=(W*1.5e-6) \

ps=((2*1.5e-6)+W) pd=((2*1.5e-6)+W) region=sat

subckt P_def (d g s b)

parameters L=lmin W=wmin

M0 (d g s b) P w=W l=L as=(W*1.5e-6) ad=(W*1.5e-6) \

ps=((2*1.5e-6)+W) pd=((2*1.5e-6)+W) region=sat

```

BR 8/02 6

### pmeas.va, delta probe.def

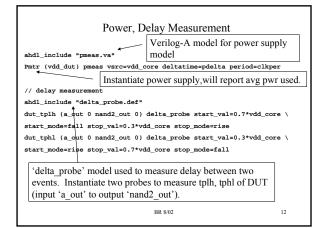

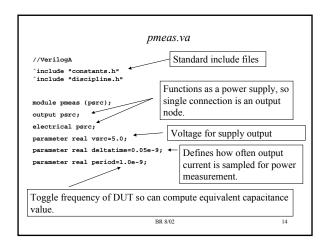

- pmeas.va is a Verilog-A model that implements a power supply that reports average power usage

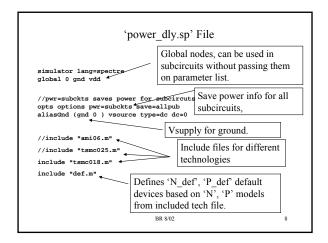

- Included by power dly.sp which is the top level Spice file

- delta\_probe.def is a Spectre HDL model that implements a probe for measuring delay between two events

- Included by power\_dly.sp which is the top level Spice file

- Provided in the sample Analog HDL model library in the Cadence distribution

- A very flexible model, look at the source code for more documentation or Appendix D in the Verilog-A language reference guide. Very similar in capability to the HSPICE '.measure' statement if you are used to that.

BR 8/02

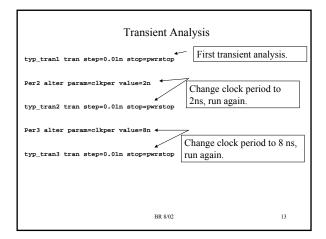

### Parameter Definitions

parameters vdd\_core=3.3 vss\_core=0.0

parameters tr=.1n tf=.1n

parameters cload=15f

parameters pdelta=0.05n

parameters clkper=4n

parameters pwrstop=10\*clkper

Should use parameter definitions for constant values – makes it easier to experiment with different values.

BR 8/02

```

Subcircuit Definitions

Using lmin, wmin so

// lmin, wmin defined in model file

can experiment with

subckt NAND2X1 A B Y vddc gndc

M3 (Y A net29 gndc) N_def w=2*wmin l=1min

different technologies.

M4 (net29 B gndc gndc) N_def w=2*wmin l=lm

M2 (Y B vddc vddc) P_def w=2*wmin l=lmin

M1 (Y A vddc vddc) P def w=2*wmin l=lmin

s NAND2X1

ibekt INVX1 A Y vddc gndc

M2 (Y A gndc gndc) N_def w=wmin l=lmin

M1 (Y A vddc vddc) P_def w=2*wmin l=lmin

s INVX1

Using N def, P def so

that default values for

ends INVX1

AS, AD, PS, PD are

subckt INVX4 A Y vddc gndc

M2 (Y A gndc gndc) N_def w=wmin*4 l=lmin

M1 (Y A vddc vddc) P_def w=2*wmin*4 l=lmin

calculated from W,L.

ends INVX4

Passing in nodes for Vdd, Gnd so that power

supplies can be kept separate for power tracking.

10

```

# Sources, Circuit Instantiation v\_vdd (vdd gnd) vsource type=dc dc=vdd\_core vpulse1 (a gnd) vsource type=pulse val0=vss\_core val1=vdd\_core period=clkper rise=tr fal1=tf width=clkper/2 Clock source for input node. Driver (a a\_out vdd gnd) INVX1 Dut (a\_out vdd nand2\_out vdd\_dut gnd) NAND2X1 Load (nand2\_out nand2\_out) vdd gnd) INVX4 Instantiate driver, dut, and load cells. Note that dut has a separate power supply (defined later in file).

```

pmeas.va (cont.)

integer numsteps;

Internal variables.

real avg_pwr,real cap, i_sum ;

analog begin

@(initial_step)

Triggered once at time=0, initialize

i_sum = 0.0;

avg_pwr = 0.0;

variables.

numsteps = 0;

Triggered every deltatime, keep

@(timer(0, deltatime))

output current sum, and # of steps.

i_sum = i_sum + I(psrc);

numsteps = numsteps + 1;

Triggered at simulation end, compute/print

end;

average power, capacitance.

@(final_step) begin

avg_pwr = (i_sum*vsrc)/numsteps;

cap = avg_pwr*period/(vsrc*vsrc);

$display("%M: Avg pwr = %g, Capacitance: %g\n",avg_pwr, cap);

Assign output voltage.

V(psrc) <+ vsrc; ←

end

15

```

# Running Spectre

- % swsetup ncsu-cadence

- % spectre power\_dly.sp

When running Spectre, will get several warnings about switching between Spice input mode and Spectre input mode – this is ok.

Will also get a warning about 'Only one connection found to node 0'. Node '0' is the default node name for ground – we use the 'gnd' power supply for this, so this warning can be ignored.

BR 8/02 16

### Spectre Output Not all Spectre output is shown, only part of it. Transient Analysis `typ\_tranl': time = (0 s -> 40 ns) ......9......8...........7........6....... Pmtr: Avg pwr = -6.71038e-05, Capacitance: -2.46479e-14 Number of accepted tran steps = 1582. Initial condition solution time = 10 ms. Output from 'pmeas' model. Intrinsic tran analysis time = 1.19 s. Module instance: dut\_tphl + Start argument = 2.18142721893e-09 s. Stop argument = 2.23273276011e-09 s. Output from 'delta probe' instances. Delta = 5.13055411827e-11 s. dule instance: dut\_tplh Start argument = 7.69079045269e-11 s. Stop argument = 1.40853531626e-10 s. Delta = 6.3945627099e-11 s. Total time required for tran analysis `typ\_tran1' was 1.2 s. BR 8/02

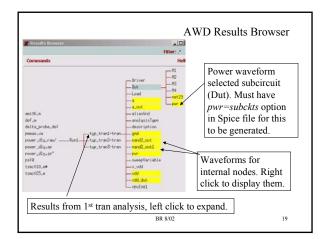

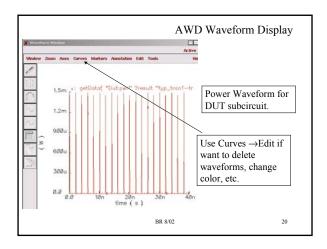

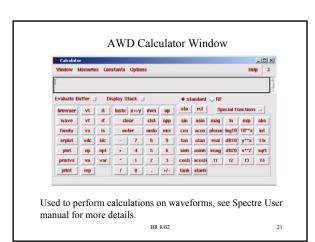

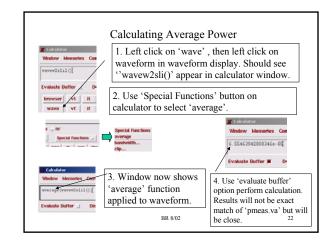

# Waveform Display

Output data is placed in power dly.raw/ directory.

The waveform display tool is called 'awd'.

To start waveform viewer, do:

% awd -dataDir power\_dly.raw

This will open several windows. Chapter 2 of the Spectre User Guide has a good introduction to 'awd' usage.

BR 8/02 18

# General Notes on Simulation

- Use waveform display for debugging, use probes, models for measuring values

- Much faster, repeatable

- Question your results i.e, if you get a power in 10's of watts or delay in microseconds, something is probably wrong

- In reports, don't use more than 3 significant digits.

Providing an answer like 67.0332459 is meaningless.

- Do not wait until the last minute most simulation assignments will take multiple tries.

BR 8/02

23