## Inverter Switching Point

• The inverter switching point is determined by the ratio of the *Bn/Bp*, where *Bn* is the gain of the N-tree and *Bp* is the gain of the P-tree.

- If Bn/Bp = 1, then switching point is Vdd/2

- If the W/L of both N and P transistors are equal, then  $Bn/Bp = \mu_n/\mu_p$  = electron mobility/hole mobility

- This ratio usually between 2 and 3

- This means that ratio of the Wptree / Wntree needs to be between 2 and 3 in order for Bn/Bp to be approximately 1

- In this class will use W<sub>ptree</sub>/W <sub>ntree</sub>to be 2

BR 9/00

15

Gate Sizes Assume minimum sized inverter is Wp/Wn = 2/1, L= Lmin. Wn = Lmin, Wp = 2\* Lmin. This becomes the 1X inverter for this technology. 1X inverter lx In a standard cell library, will have different sized gates to choose from for increasing loads Wp/Wn still = 2/1, but Wp, Wn are double the size used in 1X inverter. For most gates, diminishing 3x returns after about 4x. BR 9/00 16

## What affects gate delay? Environment Vdd – increasing VDD decreases delay - Temperature - decreasing Temp decreases delay - Fabrication effects - Fast NMOS, Fast PMOS, Slow NMOS, Slow PMOS Usually measure delay for at least three cases - Best - high Vdd, low Temp, Fast N, Fast P (use high Vdd, Low temp only if these conditions can adversely affect the circuit operation, e.g. timing margin for hold time is affected by fastest paths, not slowest paths). - Worst - low Vdd, high Temp, Slow N, Slow P - used for determining timing margin purposes. - Nominal - nominal Vdd, Room Temp (25 C), nominal N,P BR 9/00 21

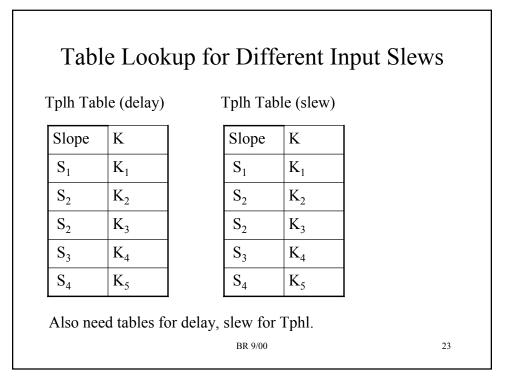

| 4              | 2D Table          | Based of          | n Cload            |

|----------------|-------------------|-------------------|--------------------|

|                | Cload             |                   |                    |

| Slope          | 1X CL             | 5X CL             | 15x CL             |

| S <sub>1</sub> | K <sub>1_1x</sub> | K <sub>1_5x</sub> | K <sub>1_15x</sub> |

| $S_2$          | K <sub>2_1x</sub> | K <sub>2_5x</sub> | K <sub>2_15x</sub> |

| S <sub>3</sub> | K <sub>3_1x</sub> | K <sub>3_5x</sub> | K <sub>3_15x</sub> |

| $S_4$          | K <sub>4_1x</sub> | K <sub>4_5x</sub> | K <sub>4_15x</sub> |

| $S_5$          | K <sub>5_1x</sub> | K <sub>5_5x</sub> | K <sub>5_15x</sub> |

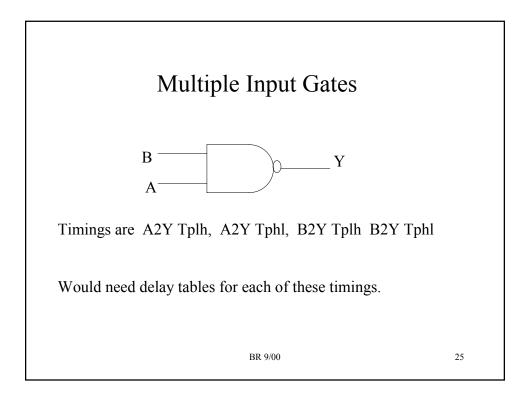

Would need four tables for Tplh (delay), Tplh (slew), Tphl (delay), Tphl(slew)

BR 9/00

24

| :                              | System Power Consumption                                                                                                                                          |         |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| System Pd =                    | = Static + Dynamic                                                                                                                                                |         |

| Static = prop<br>be a constant | portional to number of transistors in system                                                                                                                      | n (will |

| Dynamic =                      | Capacitance switched at clock frequency<br>net, FF clock loads ) +                                                                                                | (clock  |

|                                | Capacitance switched at compute rates (combinational gates)                                                                                                       |         |

| toggle rates a clock frequer   | binational gates switch with each calculation<br>are typically anywhere from 5% to 15% of<br>ncy. Logic synthesis techniques can be us<br>aggle rate of a system. | the     |

|                                | BR 9/00                                                                                                                                                           | 30      |

## CMOS Technology Scaling

- See page 146-149 of Rabaey text

- Full Scaling Vdd scaled by S, Dimensions by S

- General Scaling Vdd scaled by U, Dimensions by S

- Fixed-Voltage Scaling only Dimensions by S

- Overall Capacitance scales by 1/S, all scaling models

- Delay by 1/S (short channel devices, all scaling models)

BR 9/00

33