## Input Output Buffer Information Specification (IBIS)

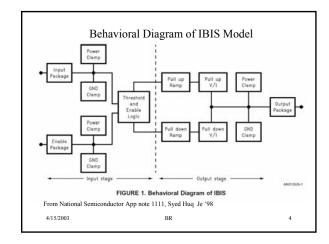

- Problem: Want to model transmission line effects and other signal integrity issues on boards for different packages/buffer combinations

- · Need models for packages/buffer structures

- Want models to keep underlying implementation details hidden because of proprietary nature of I/O drivers

- Need models to be usable by a variety of simulators and freely interchangeable

- Need simulator that understands IBIS models or else a translation mechanism that converts an IBSI model to my simulator model format.

4/15/2003 BR 1

## **IBIS Standard**

- V1.0 1993, V3.2 Sept. 1999, V4.0 July 2002

- Table driven format using V/I curves for buffers, key specs like R/L/C of package pins

- · Offers Fast, Accurate Signal Integrity simulation

- Standalone signal integrity products from Cadence, Mentor Graphics (HyperLynx) can read IBIS models directly

- · HSPICE (Synopsys) can read IBIS models directly

4/15/2003 BR 2

## Model Types

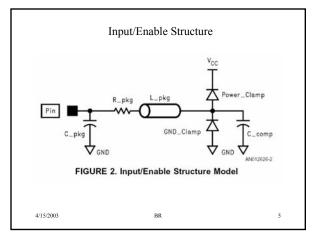

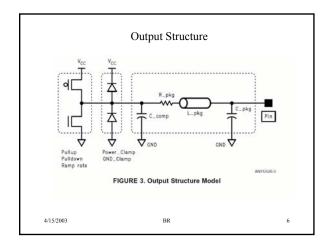

- Input, Output, I/O, 3-state, Open\_drain, I/O\_open\_drain,

- Open\_sink, I/O\_open\_sink, Open\_source, I/O\_open\_source,

- Input\_ECL, Output\_ECL, I/O\_ECL, 3-state\_ECL, Terminator,

- · Series, and Series\_switch.

4/15/2003 BR