## JEDEC File Reader

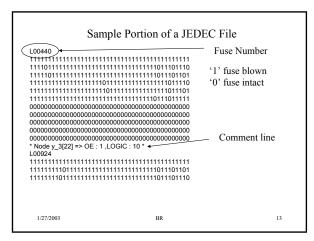

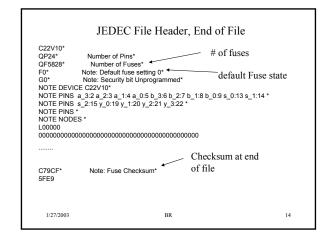

- utilities directory has a JEDEC file reader package (jedec\_reader)

- Independent of PAL type being modeled

- Approach is to read the JEDEC file and return a bit\_vector of fuse values

- '0' means connected (fuse intact), '1' is disconnected (fuse blown)

- Handles the following record types

- 'L' fuse list

- 'Q' number of total fuses in device needed to allocate fuse array

- 'F' default fuse state, used to fill fuse array with default state

- 'C' checksum record, reads this but does nothing with it.

- · Other records ignored

1/27/2003

```

BR

```

Modeling a Programmable Part: Approaches · Approach #1: have internal data structure that represents the entire programmable substrate - Read programming bits from external data file and "program" data structure to have needed routing and logic functionality - Model simply exercises programmable substrate with the presence of programming data - Perhaps most accurate simulation since it is closest to the hardware - execution time, memory requirements may be steep • Approach #2: have an external model 'generator' ( i.e. a Perl script) that reads the programming bits and generates only the functionality needed - Memory, execution time resources will be proportional to the percentage of the programmable device actually used 1/27/2003 BR 16

## Modeling Functionality

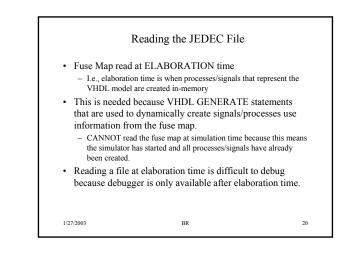

- JEDEC reader returns a bit vector whose size is equal to the number of fuse locations

- This model uses the GENERATE statement in VHDL to create a model whose memory and runtime complexity is proportional to the number of fuses that are programmed

Model will take less memory space and run faster if less of the

- device is actually programmed

- GENERATE statement allows processes/signals to be generated at model elaboration time

- somewhat similar to a macro capability in other languages

1/27/2003

BR

17

15

## Compilation/Elaboration/Execution Compilation converts VHDL text to simulator dependent object code Elaboration is what happens when the model is loaded into memory Initial processes/signal structures are created in memory

- GENERATE statements can be used to create signals and processes based upon parameters during elaboration.

This is a very powerful language feature.

- *Execution* happens after elaboration, and is the simulation loop of scheduling events and executing processes.

```

1/27/2003

```

BR

18

| Product Term Modeling Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |  |  |  |

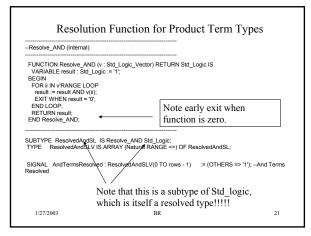

| Use a <i>resolved</i> data type for product term (column signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |  |  |  |

| are simply multiple drivers on the product term)<br>Read fuse map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |  |  |  |

| CONSTANT FuseMap : Bit_Vector := ReadJedec(JedecFileName);<br>CONSTANT rows :: Natural := 64;<br>CONSTANT columns : Natural := 82;<br>CONSTANT outputs : Natural := 8;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |  |  |  |

| SUBTYPE ResolvedAndSL IS Resolve_AND Std_Logic;<br>TYPE ResolvedAndSLV IS ARRAY (Natural RANGE <>) OF ResolvedAndSL;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |  |  |  |

| SIGNAL AndTermsResolved : ResolvedAndSLV(0 TO rows - 1)         := (OTHERS => '1');And Terms ResolvedSIGNAL AndTerms : Std_Logic_Vector(0 TO owns - 1);And Terms           SIGNAL i         : Std_Logic_Vector(0 TO columns - 1);Column Inputs           SIGNAL OrTerms : Std_Logic_Vector(0 TO outputs - 1);Column Inputs        Column InputsColumn InputsColumn InputsColumn InputsColumnColumnColumn InputsColumnColumnsColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumnColumColumnColumnColumnColumnColumnColum | d |  |  |  |

| Model is for pal16L8 – fuse locations, # inputs, etc are all                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |  |  |  |

| dependent on this PAL type.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |  |  |  |

| 1/27/2003 BR 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |  |

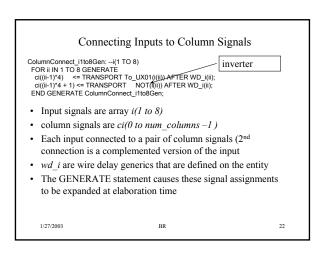

| Product Term Connections                                                                                                                                                                                                                                                                                                                        |                                                             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| ColumnConnect_i1to8Gen:i(1 TO 8)                                                                                                                                                                                                                                                                                                                |                                                             |  |  |  |

| And Plane                                                                                                                                                                                                                                                                                                                                       |                                                             |  |  |  |

| AndPlaneGen:<br>FOR row IN AndTermsResolved'RANGE GENERATE<br>RowAllConnected(Gen):<br>IF (RowAllConnected(row)) GENERATE<br>AndTermsResolved(row) <= 10; <<br>END GENERATE RowAllConnectedGen;<br>RowHoAllConnectedGen:<br>IF (NOT RowAllConnectedGen:<br>IF (NOT RowAllConnected(row)) GENERATE<br>ColumnGen:<br>FOR col IN cirkANGE GENERATE | Reduces # of signal<br>assignments, improves<br>performance |  |  |  |

| ConnectGen:<br>IF (FuseMap(row * ci'LENGTH + col) = connected) G                                                                                                                                                                                                                                                                                | GENERATE                                                    |  |  |  |

| AndTermsResolved(row) <= ci(col);                                                                                                                                                                                                                                                                                                               | Only generated if fuse<br>map location = '0'!!              |  |  |  |

| 1/27/2003 BR                                                                                                                                                                                                                                                                                                                                    | 23                                                          |  |  |  |

| Re                                                                                                                                                                                    | wAllConnected Func              | tion                       |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------|--|--|

| Recall that if all column inputs are connected to a product term,<br>then product term output is '0'. Can reduce model complexity<br>(memory and execution time) if detect this case. |                                 |                            |  |  |

| RowAllConnected (Internal                                                                                                                                                             | )                               |                            |  |  |

| FUNCTION RowAllConnected (row : Natural) RETURN Boolean IS                                                                                                                            |                                 |                            |  |  |

| BEGIN<br>RETURN NOT To_Boolea                                                                                                                                                         |                                 |                            |  |  |

|                                                                                                                                                                                       | FuseMap(row*columns             | TO (row+1)*columns - 1))); |  |  |

| END RowAllConnected;                                                                                                                                                                  |                                 |                            |  |  |

| _                                                                                                                                                                                     | n defined in VHDL for bit       | _                          |  |  |

| returns a '1' if any l                                                                                                                                                                | bit in bit vector is a '1', els | e returns                  |  |  |

| ʻ0'.                                                                                                                                                                                  |                                 |                            |  |  |

| 1/27/2003                                                                                                                                                                             | BR                              | 24                         |  |  |

## Model Complexity

- Model complexity is proportional to memory required and execution time

- The number of signals, signal assignments, and processes in a model impacts complexity

- More signals and signal assignments means more events means more execution effort required

- More signals means more memory needed to track waveform history

- Use of GENERATE statements only creates the required signal assignments for the product terms based upon the fuse map contents

BR

1/27/2003

25

| OR Terms                                                                                        |                                   |                                                               |  |  |  |

|-------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------|--|--|--|

| std_logic_vector<br>NowAndTerms gets re<br>AndTerms <= Std_Logic                                | ResolvedAndSLV type               | Can do 'type cast'<br>without explicit<br>conversion function |  |  |  |

| -Or Plane<br>OrPlaneGen:<br>FOR ii IN OrTerms'RAN<br>OrTerms(ii) <= Reduce<br>END GENERATE OrPh | e_OR(AndTerms((ii*8 + 1) TO (ii*8 | efined for                                                    |  |  |  |

| 1/27/2003                                                                                       | BR                                | 26                                                            |  |  |  |

| TriStates_1to6Gen:<br>FOR ii IN 1 TO 6 GENERATE<br>PROCESS (0rTerms(ii), AndTerms(ii*8))                                                                           | Tri-State Buffers                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|

| ALIAS i : Std_Logic IS OrTerms(ii); "<br>ALIAS oe : Std_Logic IS AndTerms(ii*8);<br>ALIAS o : Std_Logic IS io(8-ii);<br>ALIAS LD_o : Time IS LD_io(8-ii);<br>BEGIN | <i>GENERATE</i> statements can be used for processes |  |  |  |

| CASE oe IS<br>WHEN '0' =>TriStated Output<br>IF (oe'EVENT) THEN<br>o <= TRANSPORT 'X' AFTER 0 N<br>'Z' AFTER (t.ter + LD_0);                                       |                                                      |  |  |  |

| END IF;<br>WHEN'1' =>-Ouput Enabled (NOTE INVERTED)<br>IF (oe'EVENT) THEN<br>o <= TRANSPORT 'X' AFTER 0 NS,<br>NOT I AFTER (ttea + LD_o);                          |                                                      |  |  |  |

| ELSE<br>IF ((ttpd + LD_0) < (ttea + LD_0 - oe'LAST_EVENT)) THEN<br>o <= TRANSPORT NOT i AFTER (ttea + LD_0 - oe'LAST_EVENT);<br>ELSE<br>ELSE                       |                                                      |  |  |  |

| o <= TRANSPORT NOT i AFTER (t.tpd + LD_o);<br>END IF;<br>END IF;<br>WHEN OTHERS => o <= TRANSPORT oe AFTER tpdX;<br>END CASE:                                      |                                                      |  |  |  |

| END PROCESS;<br>END GENERATE TriStates_1to6Gen;                                                                                                                    |                                                      |  |  |  |