## Serializer Module

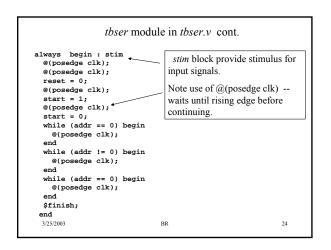

- Should wait until start is asserted

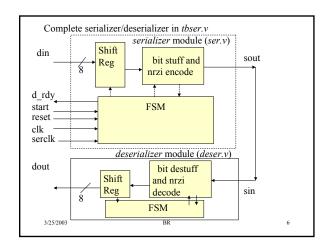

- · Send value on din serially over sout

- Request new value on din by asserting d rdy

- In testbench, there is a clock cycle latency between assertion of d rdy and a new din value being provided

- · Continually send serial data until reset is asserted.

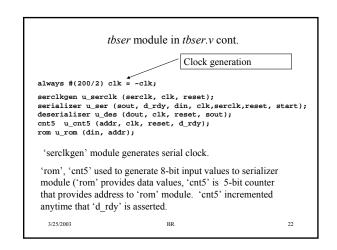

- Main clock is signal *clk*. The serial clock is *serclk* which has 1 clock pulse for every 4 pulses on clk.

- New serial data should be provided for every pulse on serclk.

BR

- Both clk and serclk provided by testbench.

3/25/2003

## Zip Archive serial.zip

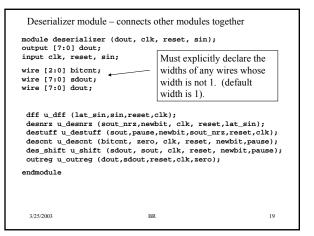

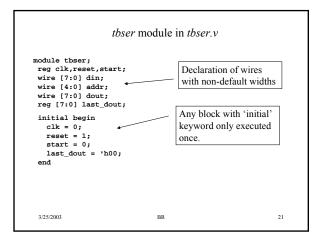

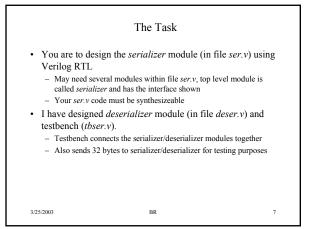

- · Contains directory serial, which contains files tbser.v, ser.v, deser.v.

- Also contains a Modelsim golden waveform called serial\_vsim.wlf and command file serial\_wave.do To view this waveform do:

- qhsim-view serial\_vsim.wlf-do "do serial wave.do"

- Shows all signals in tbser.v from golden simulation.

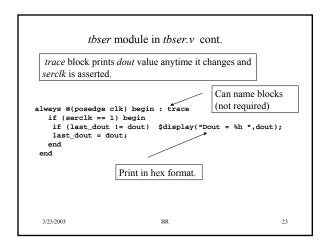

- The file qhsim\_gold\_log.txt contains the golden output - Testbench just sends 32 bytes to serializer/deserializer

- Each time a new byte comes out of the deserializer, it is printed to screen

- · Synopsys script file ser.script for testing if verilog code is synthesizeable.

- Your synthesized gate level code must produce same result as RTL code BR

9

3/25/2003