|

Dear,

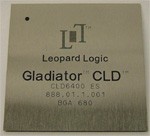

Leopard Logic, Inc. is pleased to announce the successful

qualification of the Gladiator CLD6400, the first member of the ground

breaking Gladiator CLD family of user configurable logic devices. The only

devices on the market to combine FPGA flexibility with ASIC efficiency,

Gladiator CLDs provide significant performance, power and cost advantages

over traditional FPGA and ASIC technologies by utilizing an innovative

combination of patented field-programmable (FP) and mask-programmable (MP)

fabrics.

Gladiator CLD Silicon Qualified

As the first device of the family, Gladiator CLD6400 has been

available for customer designs since spring, and has now successfully

completed functional testing and qualification for important parameters,

required for the correlation of the timing libraries to the actual silicon

performance. This correlation enables users to accurately predict device

performance based on the ToolBlox design tools and to achieve timing

closure at their desktop within hours and without the need for lengthy and

expensive design iterations needed for ASIC-like device

architectures. As the first device of the family, Gladiator CLD6400 has been

available for customer designs since spring, and has now successfully

completed functional testing and qualification for important parameters,

required for the correlation of the timing libraries to the actual silicon

performance. This correlation enables users to accurately predict device

performance based on the ToolBlox design tools and to achieve timing

closure at their desktop within hours and without the need for lengthy and

expensive design iterations needed for ASIC-like device

architectures.

The first several customer designs from technology leaders have

successfully been mapped into the CLD6400 and are targeting networking,

wireless and video applications. First production shipments to customers

are scheduled for delivery for Q3, 2004.

Click

here for the full press release.

|

|

Gartner's Brian Lewis Sees Platform ASICs Taking

Off |

|

| Gartner Dataquest Inc. presented its annual

forecasts for the industries at the 41st Design Automation

Conference (DAC) in San Diego (June 7-11, 2004). Bryan Lewis, vice

president and chief analyst at Gartner Dataquest, noted that the

semiconductor industry is expected to grow by 24.7 percent in 2004.

But he said design costs must decrease if designers are to continue

to use ASICs. That includes not only mask costs but also engineering

costs, which can be many times higher.

The good news, Lewis said, is that "platform

ASICs" are starting to take off, a trend that could ultimately

reverse the decline in ASIC design starts that has been under way

since 1997. "The whole platform concept is answering the call," he

said. "The ASIC market is not dead."

Most platform ASICs are what Dataquest calls

array- based platforms, also known as structured ASICs. Lewis

predicted the total available market for such parts would grow from

$99 million in 2004 to $848 million in 2007. Other types of platform

ASICs include devices with PLD cores and devices with cell-based

custom- logic cores. In all cases, at least 50 percent of the design

is reused. To

read the complete article click here »

|

|

|

AccelChip & L.L.I Join Forces to Target DSP

Market |

|

AccelChip Inc., the industry's

only provider of automated flows from MATLAB algorithms to silicon,

has selected Leopard Logic as the latest participant in its

AccelChip Silicon vendor Alliance Program (ASAP). Under this

agreement AccelChip DSP Synthesis tools will be extended to support

Leopard Logic's Gladiator CLD configurable logic devices to offer

mutual customers a complete DSP flow that allows them to take

designs seamlessly from FPGA prototyping into production using

Gladiator CLD. AccelChip Inc., the industry's

only provider of automated flows from MATLAB algorithms to silicon,

has selected Leopard Logic as the latest participant in its

AccelChip Silicon vendor Alliance Program (ASAP). Under this

agreement AccelChip DSP Synthesis tools will be extended to support

Leopard Logic's Gladiator CLD configurable logic devices to offer

mutual customers a complete DSP flow that allows them to take

designs seamlessly from FPGA prototyping into production using

Gladiator CLD.

"The Gladiator CLD family is the first device

that combines FPGA and ASIC logic into a fully user-customizable

device. In addition to this innovative architecture, Leopard Logic

has done an outstanding job putting together a comprehensive RTL

flow to support it," said Dan Ganousis, president and CEO of

AccelChip Inc. "By working with AccelChip, they are now able to

extend this flow into the DSP market without incurring the

development expenses for a proprietary flow." Click

here for the full press release »

|

|

|

True Circuits Provides Silicon Proven IP for Gladiator

CLD |

|

True Circuits, Inc., a leading provider of

analog and mixed-signal intellectual property (IP) for the

semiconductor, systems and electronics industries, and Leopard Logic

announced the successfull implementation of multiple True Circuits

PLL and DLL hard macros in the Gladiator CLD family of configurable

logic devices. True Circuits, Inc., a leading provider of

analog and mixed-signal intellectual property (IP) for the

semiconductor, systems and electronics industries, and Leopard Logic

announced the successfull implementation of multiple True Circuits

PLL and DLL hard macros in the Gladiator CLD family of configurable

logic devices.

"With its Gladiator CLD approach, Leopard Logic

combines the flexibility of FPGAs with the efficiency of ASICs for

high speed, high density, low per-gate cost and low power

applications," remarked John G. Maneatis, President of True

Circuits. "We are pleased to be a contributor to this unique design

and family of programmable devices, and to help our customers

achieve success with our low-jitter, programmable PLLs and DLLs in

their high-performance design applications." Click

here for the full press release »

|

| Quick Links... |

|

|

![]()